## Homework No. 6 – Solutions

<u>Problem 1 – P5.10</u>

$$\begin{split} t_{PLH} &= 0.7RC = R_{EQP} \frac{L}{W_{P}} C_{LOAD} \\ W_{P} &= 0.7R_{EQP} \frac{L}{t_{PLH}} C_{LOAD} = 0.7 \left(30 \times 10^{3}\right) \frac{(2\lambda)}{(50 \times 10^{-12})} \left(75 \times 10^{-15}\right) = 63\lambda \\ t_{PHL} &= RC = 0.7R_{EQN} \frac{L}{W_{N}} C_{LOAD} \\ W_{N} &= 0.7R_{EQN} \frac{L}{t_{PHL}} C_{LOAD} = 0.7 \left(12.5 \times 10^{3}\right) \frac{(2\lambda)}{(50 \times 10^{-12})} \left(75 \times 10^{-15}\right) = 26.6\lambda \approx 27\lambda \end{split}$$

Because the number of transistors in series is more than one, we must multiply the widths by the appropriate number. Here, all the NMOS transistors will have a width of  $54\lambda$ . The PMOS transistors will have widths of  $126\lambda$  and  $190\lambda$ , respectively.

<u>Problem 2 – P5.11</u>

We estimate the dc power and dynamic switching power for this problem.

a.) The circuit's dc power can be computed by computing the dc current when the output is low. This is given by  $I_{DS}$ =550uA/um x 0.1um=55uA. Then  $P_{DC}$ =66uW when the output is low.

b.) Its dynamic power can be calculated by simply using the equation  $P_{dyn} = \alpha C V_{DD}^2 f$ . Therefore,  $P_{dyn} = (50 \text{ fF})(V_{DD} - V_{TN})(V_{DD})(100 \text{ MHz}) = 4.4 \text{ uW}$ .

## <u>Problem 3 – P5.12</u>

The pseudo-NMOS inverter has static current when the output is low. We can estimate it as:

$$I_{P}(sat) = \frac{W_{P}v_{sat}C_{OX}(V_{GS} - V_{T})^{2}}{V_{GS} - V_{T} + E_{CP}L} = \frac{(0.1 \times 10^{-4})(8 \times 10^{6})(1.6 \times 10^{-6})(1.2 - 0.4)^{2}}{1.2 - 0.4 + (24)(0.1)} = 25.6\,\mu\text{A}$$

Then the average static power is  $P_{\text{stat}} = (25.6 \text{uA})(1.2)/2 = 15.4 \text{uW}$ .

The dynamic power is  $P_{dyn} = CV_{DD}V_{swing}f_{avg} = (50 \text{ fF})(1.2)(1.1)\text{ f}_{avg}$  assuming that V<sub>OL</sub> is 0.1V.

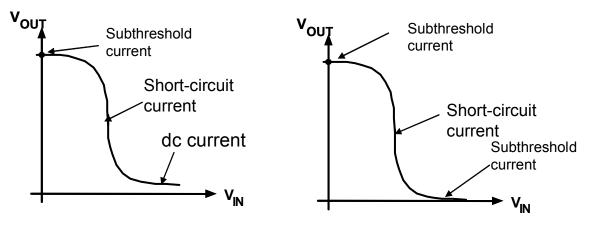

For the CMOS inverter, the static power is almost zero:  $P_{\text{stat}}=I_{\text{sub}}V_{\text{DD}}$ . It is far less than the pseudo-NMOS case. The dynamic power  $P_{dyn} = CV_{DD}V_{swing}f_{avg} = (50\text{ fF})(1.2)^2 f_{avg}$  is slightly larger than the pseudo-NMOS case.

Pseudo-NMOS CMOS Inverter

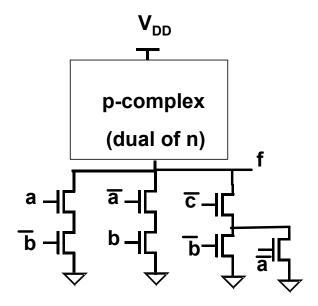

## <u>Problem 4 – P5.16</u>

The circuit is shown below. The delay should incorporate both Q and Qb settling in 400ps. All NMOS and PMOS devices are the same size in both NAND gates.

$$t_{P} = t_{PHL} + t_{PLH} = 0.7R_{UP}C_{LOAD} + 0.7R_{DOWN}C_{LOAD} = 0.7C_{LOAD} \left( R_{eqp} \frac{L_{P}}{W_{P}} + R_{eqn} \frac{2L_{N}}{W_{N}} \right)$$

$$= \frac{0.7C_{LOAD} \left( R_{eqp}L + 2R_{eqn}L \right)}{W}$$

$$W = \frac{0.7C_{LOAD} \left( R_{eqp}L + 2R_{eqn}L \right)}{t_{P}} = \frac{0.7 \left( 100 \Box 0^{-15} \right) \left( \left( 30 \Box 0^{3} \right) (0.1) + 2 \left( 12.5 \Box 0^{3} \right) (0.1) \right)}{400 \Box 0^{-12}}$$

$$\approx 1 \text{um}$$