# Homework No. 7 – Solutions

## <u>Problem 1 – P5.17</u>

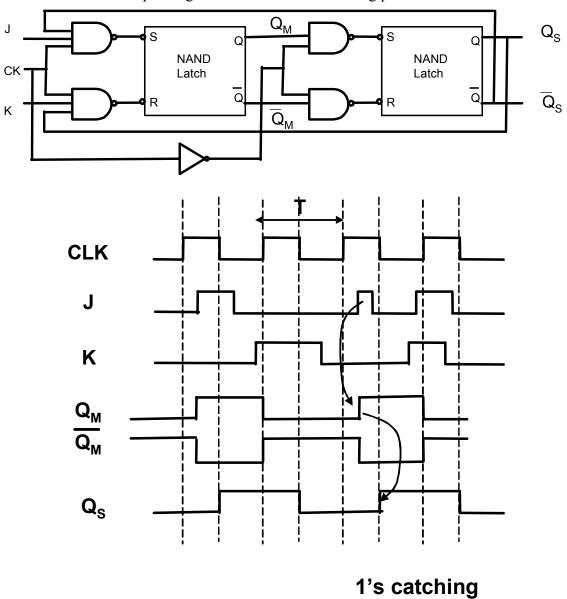

The small glitch in J propagates through the flop even though it is small. This is due to the fact that the JK-flop of Figure 5.20 has the 1's catching problem.

### <u>Problem 2 – P5.18</u>

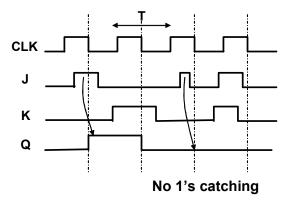

The small glitch in J does not propagate through the flop since the edge-triggered configuration does not have a 1's catching problem.

### <u>Problem 3 − P6.1</u>

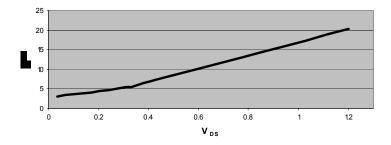

The on-resistance of a unit-sized NMOS device.

On-resistance of a unit-sized NMOS device

The average on-resistance is approximately 15k $\Omega$ . The expression for the average resistance value between  $V_{DD}$  and  $\frac{V_{DD}}{2}$ .

$$\begin{split} R_{ON} &= \frac{R_{ON} \left( V_{DD} \right) + R_{ON} \left( V_{DD} \right)}{2} = \frac{\frac{V_{DS} \left( V_{DD} \right)}{I_{DS} \left( V_{DD} \right)} + \frac{V_{DS} \left( V_{DD} \right)}{I_{DS} \left( V_{DD} \right)}}{2} = \frac{\frac{V_{DD}}{I_{D,sat}} + \frac{V_{DD} \left( V_{DD} \right)}{I_{D,sat}}}{2} \\ &= \frac{3V_{DD}}{4I_{D,sat}} = \frac{3V_{DD} \left( V_{GS} - V_T + E_{CN} L_N \right)}{4W v_{sat} C_{ox} \left( V_{GS} - V_T \right)^2} \end{split}$$

#### Problem 4 - P6.2

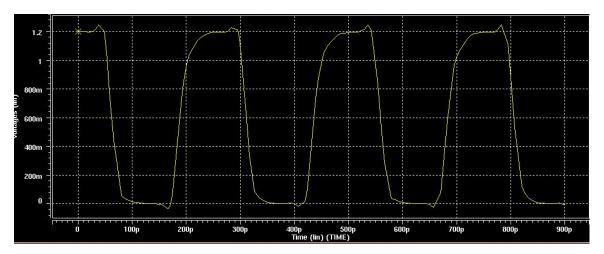

For this case, we will be comparing to SPICE so use L=0.13um. Since the signal must go around the ring twice for one oscillation, the period is :

$$t_{TOT} = N(t_{PLH} + t_{PHL}) = N(R_P C_{LOAD} + R_N C_{LOAD}) = N(R_P + R_N)(C_W W)$$

$$= N\left(R_{EQP} \frac{L}{W_P} + R_{EQN} \frac{L}{W_N}\right) (C_g + C_{eff})(W_P + W_N)$$

$$= 7\left((30 \times 10^3) \frac{1}{2} + (12.5 \times 10^3)\right) (2+1)(10^{-15})(0.4)$$

$$= 7(27.5 \times 10^3)(3 \times 10^{-15})(0.4) = 23 \text{ lps}$$

$$f = \frac{1}{t_{TOT}} = \frac{1}{231 \text{ ps}} = 4.3 \text{ GHz}$$

This is independent of inverter size. Consider the delay equation given above which is in terms of W. Since each inverter drives an identical inverter, when we increase the W of an inverter, it acts to reduce the resistance of the driver and increase the capacitance of the load by the same amount (roughly speaking, of course). Therefore, the oscillation frequency should remain constant as we increase the sizes.

The SPICE results show a period of about 250ps or a frequency of 4GHz.

#### Problem 4 - P6.4

The self-capacitance in these cases are the capacitances that will make the transition from 0 to  $V_{DD}$  or vice versa.

a. In this case, all the internal nodes will be charged so the self-capacitance is:

$$C_{SELF} = C_{eff} (2W + 2W + 3W + 3W + 3W) = 13C_{eff}W$$

b. In this case, all the internal nodes but the one above the bottom NMOS transistor will be charged:

$$C_{SELF} = C_{eff} (2W + 2W + 3W + 3W) = 10C_{eff}W$$

c. If we assume a worst-case scenario, this node will be charged up to  $V_{\rm DD}$  from 0.

$$C_{SELF} = C_{eff} (2W + 2W + 3W + 3W + 3W) = 13C_{eff}W$$

d. The node above the bottom-most NMOS transistor has already been discharged.

$$C_{SELF} = C_{eff} (2W + 2W + 3W + 3W) = 10C_{eff}W$$