## **Homework Assignment No. 8**

Due on Monday, March 14, 2005

1.) Problem P6.6 of the text.

[Answers:

$$C_4 = 203.89C_{inv}$$

,  $C_3 = 36.64C_{inv}$ ,  $C_2 = 5.89C_{inv}$ , and  $C_1 = C_{inv}$ , path delay = 25.5,  $N_{ont} = 5$ , path delay(opt) = 18.5]

2.) Problem P6.9 of the text.

[Answers: a.) 5/3, b.) 5/3, c.)

$$LE_R = 8/3$$

,  $LE_F = 2/3$  and d.)  $LE_R = 4/3$ ,  $LE_F = 2$ ]

3.) Problem P6.12 of the text.

[Ans.

$$C_4$$

= 173.21 $C_{inv}$ ,  $C_3$  = 25 $C_{inv}$ ,  $C_2$  = 11.55 $C_{inv}$ , and  $C_1$  =  $C_{inv}$ , path delay = 51.2]

4.) Problem P6.13 of the text.

[Ans.

$$C_5 = 1095.8C_{inv}$$

,  $C_4 = 175.1C_{inv}$ ,  $C_3 = 114.3C_{inv}$ ,  $C_2 = 17.5C_{inv}$ , and  $C_1 = C_{inv}$ , path delay = 88.9, optimum number of stages = 10]

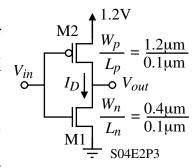

5.) The CMOS inverter shown uses  $0.13\mu m$  CMOS technology. a.) Sketch the voltage transfer characteristic of the standard CMOS inverter shown. Label the points on this curve that separate the various regions of operation for the MOSFETs. Estimate the location of these points as close as possible without numerical calculations. b.) How far can the power supply,  $V_{DD}$ , be reduced before the inverter fails to operate correctly? c.) Sketch a graph of the dc current transfer characteristic versus the input voltage for

the above inverter. Compute the peak value of current and label all important points along the characteristic.