## LECTURE 160 – BIPOLAR TECHNOLOGY (READING: Text-Sec. 2.4, 2.5)

#### **INTRODUCTION**

### **Objective**

The objective of this presentation is:

- 1.) Illustrate the fabrication sequence for a typical bipolar junction transistor

- 2.) Show the physical aspects of the BJT

#### **Outline**

- *npn* BJT technology

- Compatible pnp BJTs

- Modifications to the standard npn BJT technology

- Advanced BJT technology

- Summary

ECE 4430 - Analog Integrated Circuits and Systems

Lecture 160A – Bipolar Technology (6/22/04)

#### Page 160-2

© P.E. Allen - 2004

## *npn* BIPOLAR JUNCTION TRANSISTOR TECHNOLOGY <u>Major Processing Steps for a Junction Isolated BJT Technology</u>

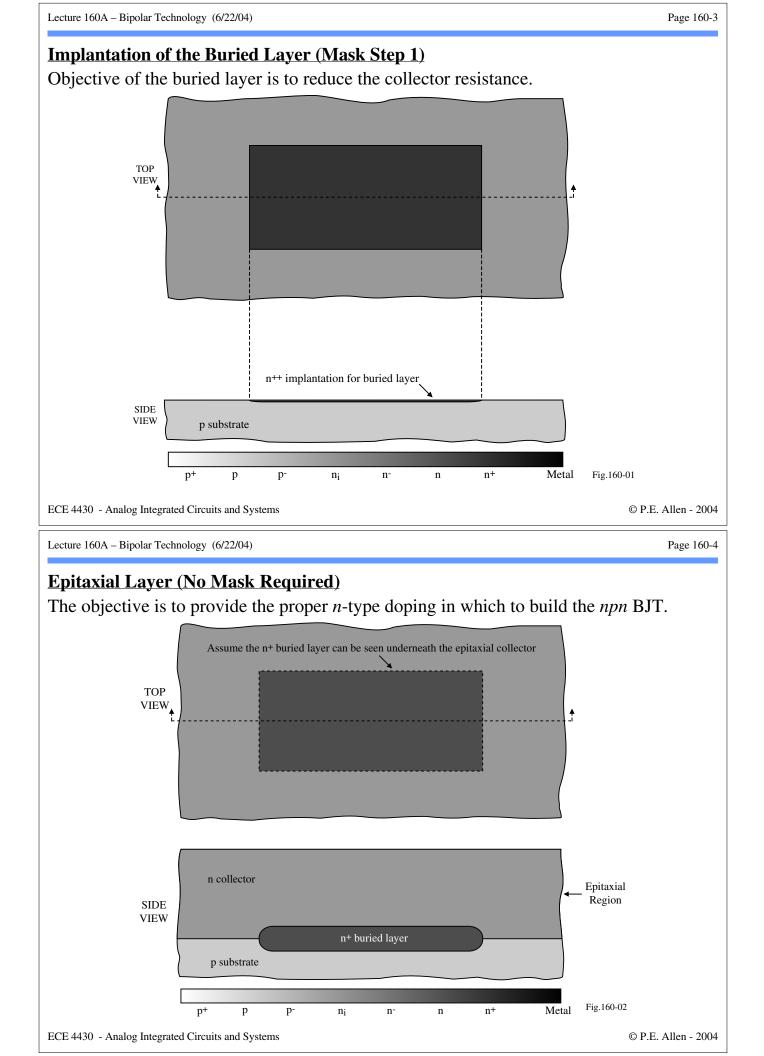

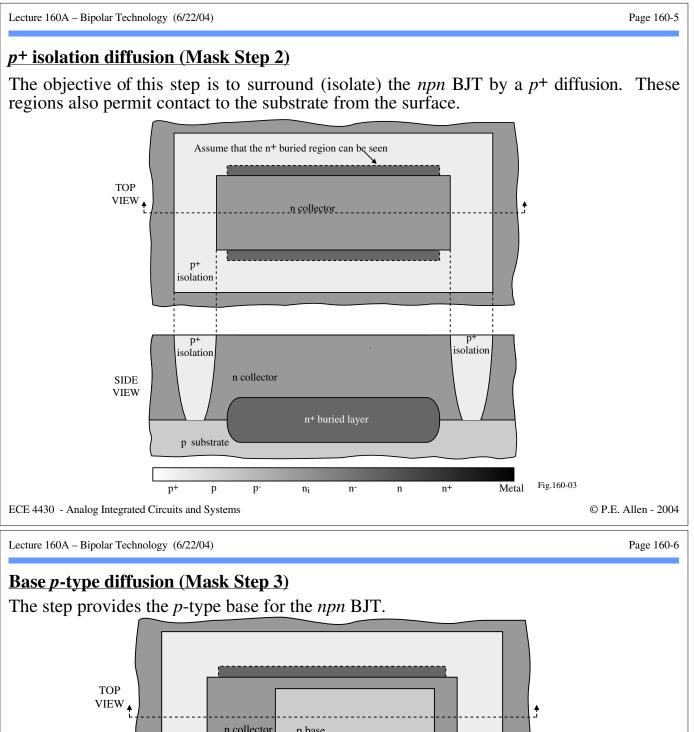

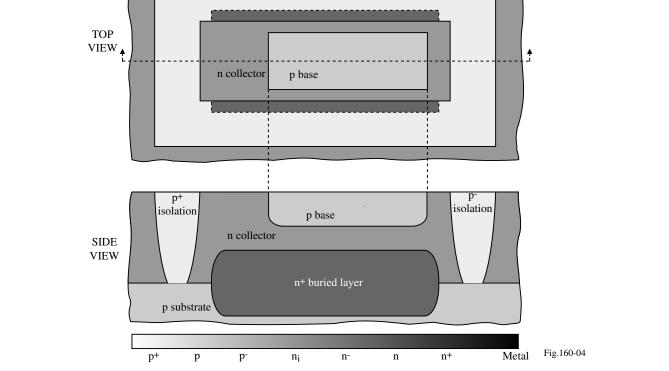

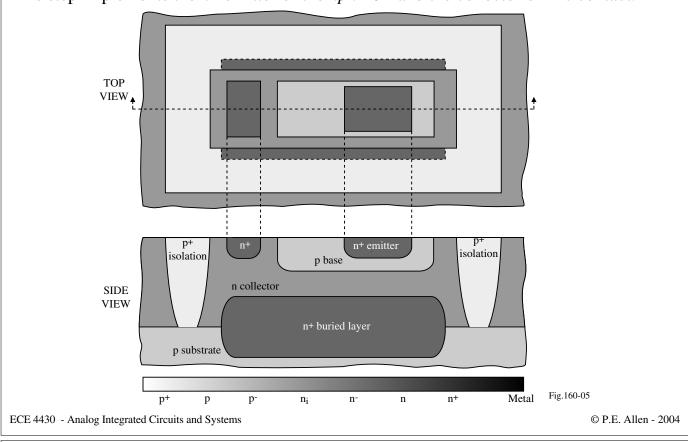

Start with a p substrate.

- 1. Implantation of the buried  $n^+$  layer

- 2. Growth of the epitaxial layer

- 3.  $p^+$  isolation diffusion

- 4. Base *p*-type diffusion

- 5. Emitter  $n^+$  diffusion

- 6.  $p^+$  ohmic contact

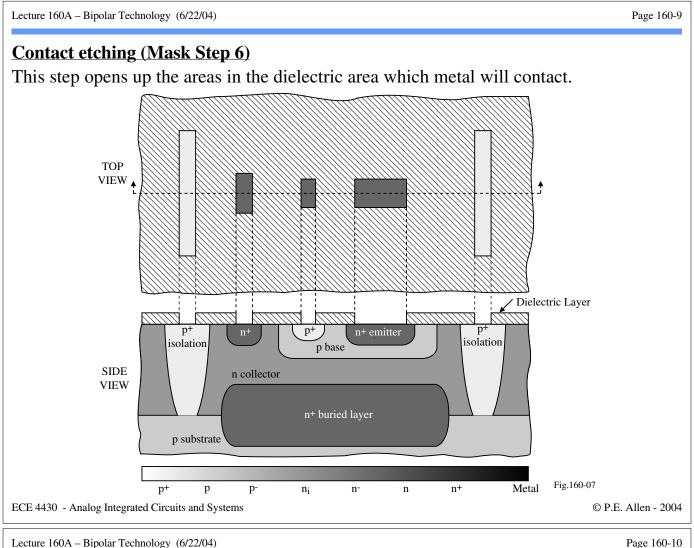

- 7. Contact etching

- 8. Metal deposition and etching

- 9. Passivation and bond pad opening

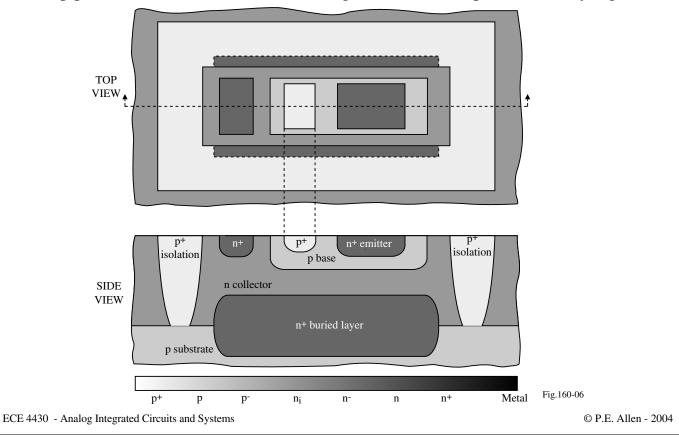

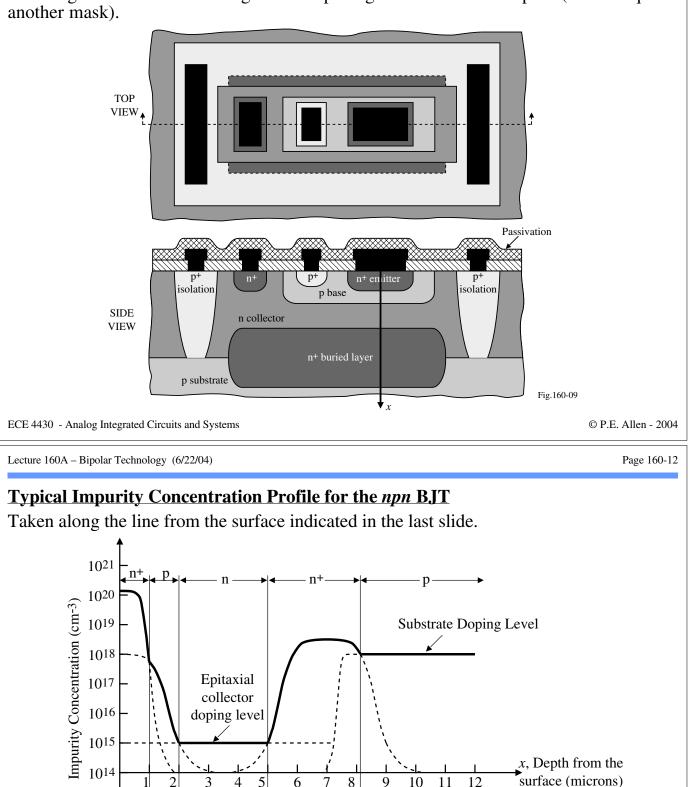

## Emitter n+ diffusion (Mask Step 4)

This step implements the  $n^+$  emitter of the npn BJT and the collector ohmic contact.

Page 160-8

## p+ ohmic contact (Mask Step 5)

Lecture 160A - Bipolar Technology (6/22/04)

This step permits ohmic contact to the base region if it is not doped sufficiently high.

#### Page 160-10

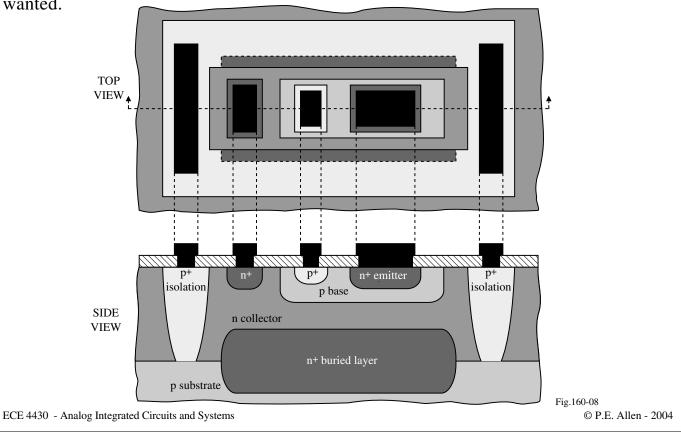

## Metal deposition and etching (Mask Step 7)

In this step, the metal is deposited over the entire wafer and removed where it is not wanted.

#### Passivation (Mask Step 8)

Covering the entire wafer with glass and opening the area over bond pads (which requires

Emitter

Base

Collector

**Buried Layer**

Substrate

1013

1012

Fig. 160-10

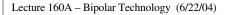

Substrate pnp BJT

### COMPATIBLE pnp BJTS

Collector is always connected to the substrate potential which is the most negative DC potential.

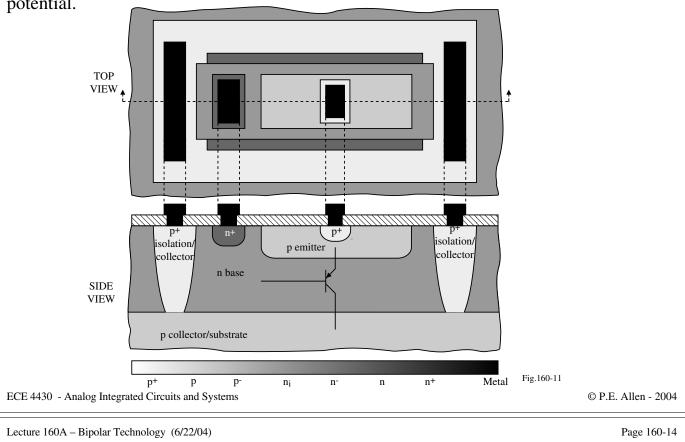

# Lateral pnp BJT

Collector is not constrained to a fixed dc potential.

Page 160-13

# MODIFICATIONS TO THE STANDARD npn TECHNOLOGY **Types of Modifications**

- 1.) Dielectric isolation Isolation of the transistor from the substrate using an oxide layer.

- 2.) Double diffusion A second, deeper n<sup>+</sup> emitter diffusion is used to create JFETs.

- 3.) Ion implanted JFETs Use of an ion implantation to create the upper gate of a pchannel JFET

- 4.) Superbeta transistors Use of a very thin base width to achieve higher values of  $\beta_F$ .

- 5.) Double diffused *pnp* BJT Double diffusion is used to build a vertical *pnp* transistor whose performance more closely approaches that of the *npn* BJT.

ECE 4430 - Analog Integrated Circuits and Systems

© P.E. Allen - 2004

Page 160-16

Lecture 160A - Bipolar Technology (6/22/04)

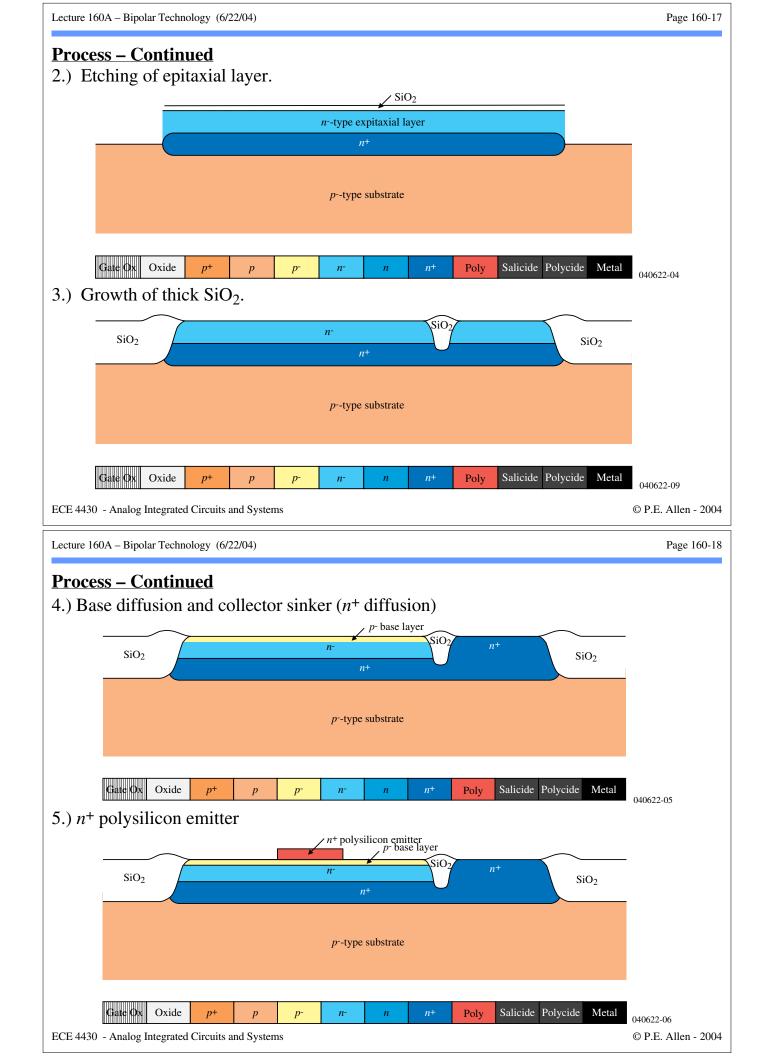

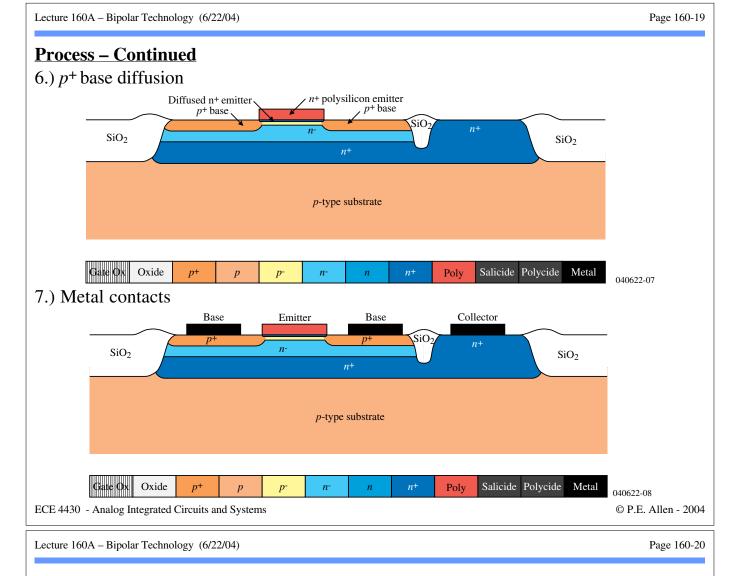

## **ADVANCED BIPOLAR IC TECHNOLOGY**

### **Objective**

Newer BJT technologies use polysilicon to form a self-aligned emitter resulting in higher frequency response capability. These technologies attempt to keep the surface of the integrated circuit as flat as possible.

## **Process**

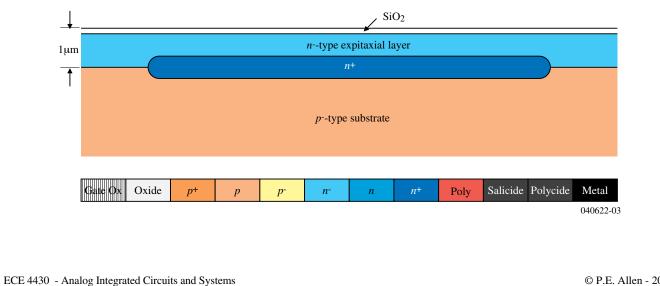

1.) Buried layer and epitaxial growth.

### SUMMARY

The objective has been to give a physical understanding of how the npn BJT is fabricated.

- The fabrication sequence for a typical npn BJT has been illustrated

- Methods of implementing other active devices in the npn BJT technology were shown.

- Simple *npn* BJT technology chooses to emphasize the *npn* over the *pnp* because the *npn* BJT performance is always superior to the *pnp* BJT performance. Thus, the philosophy in design is to use the *npn* where ever possible and incorporate the *pnp* only where it has to be used.

- An advanced BJT technology has been illustrated.

We will examine the passive components that can be implemented in a typical *npn* BJT process later.