# LECTURE 190 – CMOS TECHNOLOGY-COMPATIBLE DEVICES (READING: Text-Sec. 2.9)

### **INTRODUCTION**

## **Objective**

The objective of this presentation is examine devices that are compatible with CMOS technology

### **Outline**

- Compatible active devices the BJT lateral transistor

- Latchup and ESD

- Temperature and noise characteristics

- Summary

$ECE\,4430\,$  - Analog Integrated Circuits and Systems

© P.E. Allen - 2001

Page 190-2

Lecture 190 – CMOS Technology, Compatible Devices (10/28/01)

# **COMPATIBLE ACTIVE DEVICES**

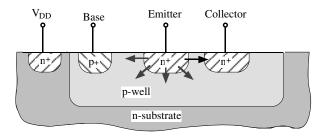

### **Lateral Bipolar Junction Transistor**

P-Well Process

NPN Lateral-

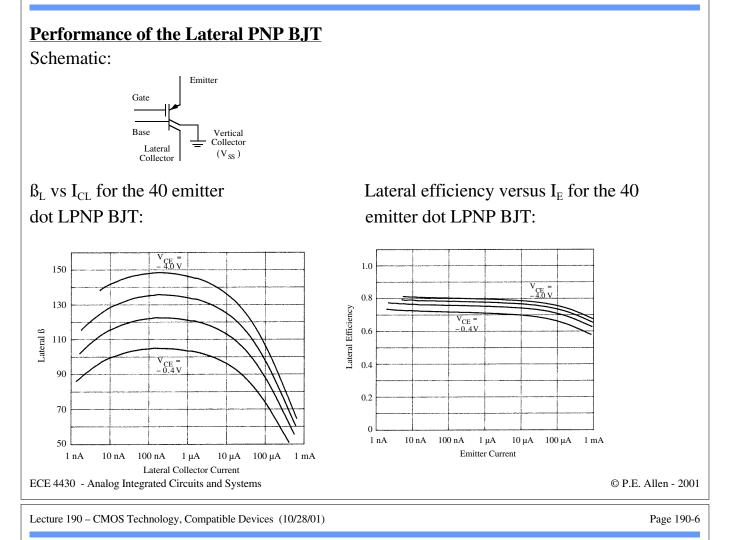

## Performance of the Lateral PNP BJT - Continued

Typical Performance for the 40 emitter dot LPNP BJT:

| Transistor area          | 0.006 mm <sup>2</sup>                                           |

|--------------------------|-----------------------------------------------------------------|

| Lateral ß                | 90                                                              |

| Lateral efficiency       | 0.70                                                            |

| Base resistance          | 150 Ω                                                           |

| E <sub>n</sub> @ 5 Hz    | 2.46 nV / <del>\(\ \  \  \  \  \  \  \  \  \  \  \  \  \ </del> |

| E <sub>n</sub> (midband) | 1.92 nV / <del>V</del> Hz                                       |

| $f_{c}(E_{n})$           | 3.2 Hz                                                          |

| I <sub>n</sub> @ 5 Hz    | 3.53 pA / <del>\/</del> Hz                                      |

| I <sub>n</sub> (midband) | 0.61 pA / <del>\/</del> Hz                                      |

| f <sub>c</sub> (In)      | 162 Hz                                                          |

| f <sub>T</sub>           | 85 MHz                                                          |

| Early voltage            | 16 V                                                            |

ECE 4430 - Analog Integrated Circuits and Systems

#### **Temperature Characteristics of Transistors**

Fractional Temperature Coefficient

$$TCF = \frac{1}{x} \cdot \frac{\partial x}{\partial T}$$

Typically in ppm/°C

MOS Transistor

$$V_T = V(T_0) + \alpha(T - T_0) + \cdots$$

, where  $\alpha \approx -2.3 \text{mV}/^{\circ}\text{C}$  (200°K to 400°K)

$$\mu = K_{\mu}T^{-1.5}$$

**BJT** Transistor

Reverse Current, I<sub>S</sub>:

$$\frac{1}{I_{S}} \cdot \frac{\partial I_{S}}{\partial T} = \frac{3}{T} + \frac{1}{T} \frac{V_{G0}}{kT/q}$$

Empirically, I<sub>S</sub> doubles approximately every 5°C increase

Forward Voltage, v<sub>D</sub>:

$$\frac{\partial v_D}{\partial T} = -\frac{V_{G0} - v_D}{T} - \frac{3kT/q}{T} \approx -2mV/^{\circ}C \text{ at } v_D = 0.6V$$

ECE 4430 - Analog Integrated Circuits and Systems

Lecture 190 – CMOS Technology, Compatible Devices (10/28/01)

#### **Noise in Transistors**

#### Shot Noise

$\overline{i^2} = 2qI_D\Delta f \text{ (amperes}^2)$ where q = charge of an electron $I_D = dc$  value of  $i_D$  $\Delta f =$  bandwidth in Hz i<sup>2</sup> Noise current spectral density =  $\overline{\Lambda f}$  (amperes<sup>2</sup>/Hz) Thermal Noise **Resistor:**  $\overline{v^2} = 4kTR\Delta f \text{ (volts}^2)$ MOSFET:  $\overline{i_D^2} = \frac{8kTg_m\Delta f}{3}$  (ignoring bottom gate) where k = Boltzmann's constantR = resistor or equivalent resistor in which the thermal noise is occurring.  $g_m$  = transconductance of the MOSFET

Page 190-12

© P.E. Allen - 2001