# LECTURE 194 – CMOS PASSIVE COMPONENTS - II (READING: Text-Sec. 2.10)

#### **Objective**

The objective of this presentation is:

1.) Examine the passive components that are compatible with CMOS technology

2.) Physical influence on passive components

#### **Outline**

- Capacitors

- Resistors

- Summary

ECE 4430 - Analog Integrated Circuit Design I

Lecture 194 – CMOS Passive Components - II (7/10/02)

#### **Capacitor Errors**

- 1.) Oxide gradients

- 2.) Edge effects

- 3.) Parasitics

- 4.) Voltage dependence

- 5.) Temperature dependence

Page 194-2

© P.E. Allen - 2002

#### **Capacitor Errors - Area/Periphery Ratio**

The best match between two structures occurs when their area-to-periphery ratios are identical.

#### Let $C'_1 = C_1 \pm \Delta C_1$ and $C'_2 = C_2 \pm \Delta C_2$

where

C' = the actual capacitance

C = the desired capacitance (which is proportional to *area*)

$\Delta C$  = edge uncertainty (which is proportional to the *periphery*)

Solve for the ratio of  $C'_2/C'_1$ ,

$$\frac{C'_{2}}{C'_{1}} = \frac{C_{2} \pm \Delta C_{2}}{C_{1} \pm \Delta C_{1}} = \frac{C_{2}}{C_{1}} \left( \frac{1 \pm \frac{\Delta C_{2}}{C_{2}}}{1 \pm \frac{\Delta C_{1}}{C_{1}}} \right) \approx \frac{C_{2}}{C_{1}} \left( 1 \pm \frac{\Delta C_{2}}{C_{2}} \right) \left( 1 \mp \frac{\Delta C_{1}}{C_{1}} \right) \approx \frac{C_{2}}{C_{1}} \left( 1 \pm \frac{\Delta C_{2}}{C_{2}} \mp \frac{\Delta C_{1}}{C_{1}} \right)$$

If  $\frac{\Delta C_{2}}{C_{2}} = \frac{\Delta C_{1}}{C_{1}}$ , then  $\left[ \frac{C'_{2}}{C'_{1}} = \frac{C_{2}}{C_{1}} \right]$

Therefore, the best matching results are obtained when the area/periphery ratio of  $C_2$  is equal to the area/periphery ratio of  $C_1$ .

ECE 4430 - Analog Integrated Circuit Design I

```

Lecture 194 – CMOS Passive Components - II (7/10/02)

```

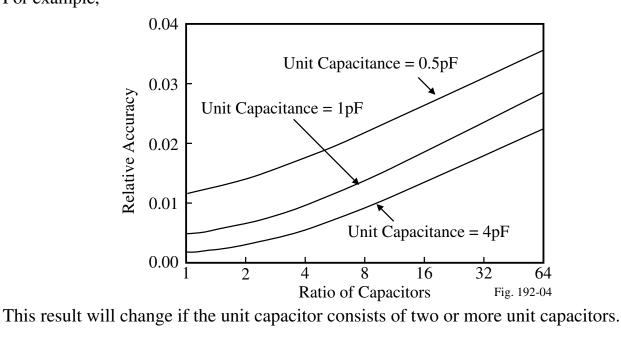

### **Capacitor Errors - Relative Accuracy**

Capacitor relative accuracy is proportional to the area of the capacitors and inversely proportional to the difference in values between the two capacitors. For example,

Page 194-6

© P.E. Allen - 2002

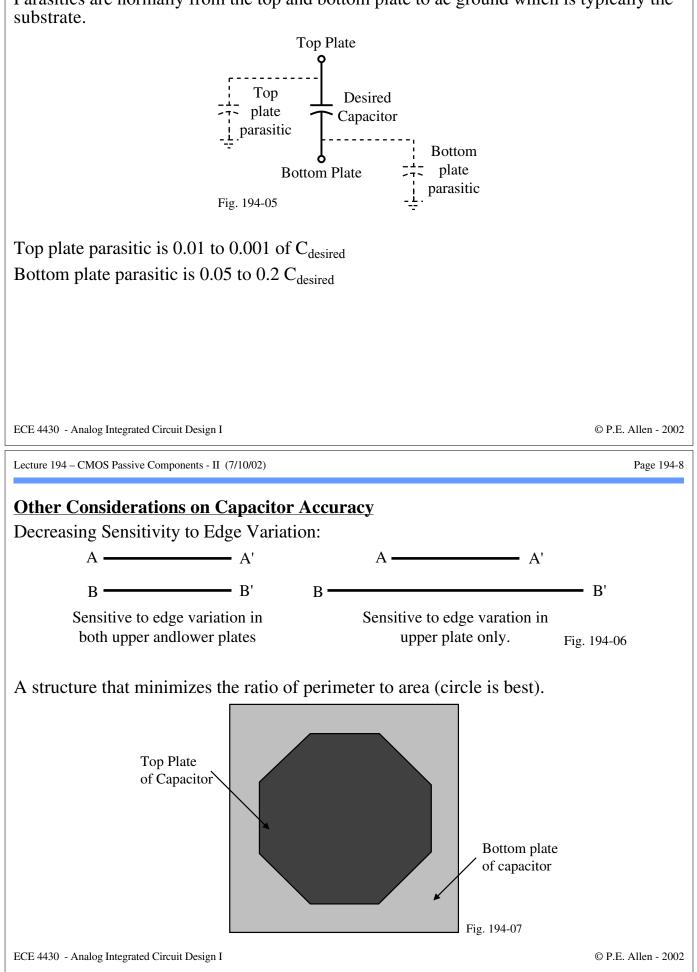

Parasitics are normally from the top and bottom plate to ac ground which is typically the

#### **Capacitor Errors - Temperature and Voltage Dependence**

Polysilicon-Oxide-Semiconductor Capacitors

Absolute accuracy  $\approx \pm 10\%$

Relative accuracy  $\approx \pm 0.2\%$

Temperature coefficient  $\approx +25 \text{ ppm/C}^{\circ}$

Voltage coefficient  $\approx$  -50ppm/V

#### Polysilicon-Oxide-Polysilicon Capacitors

Absolute accuracy  $\approx \pm 10\%$

Relative accuracy  $\approx \pm 0.2\%$

Temperature coefficient  $\approx +25 \text{ ppm/C}^{\circ}$

Voltage coefficient  $\approx$  -20ppm/V

Accuracies depend upon the size of the capacitors.

Accuracy  $\propto 1/(Area^2)$

ECE 4430 - Analog Integrated Circuit Design I

© P.E. Allen - 2002

Page 194-10

Lecture 194 – CMOS Passive Components - II (7/10/02)

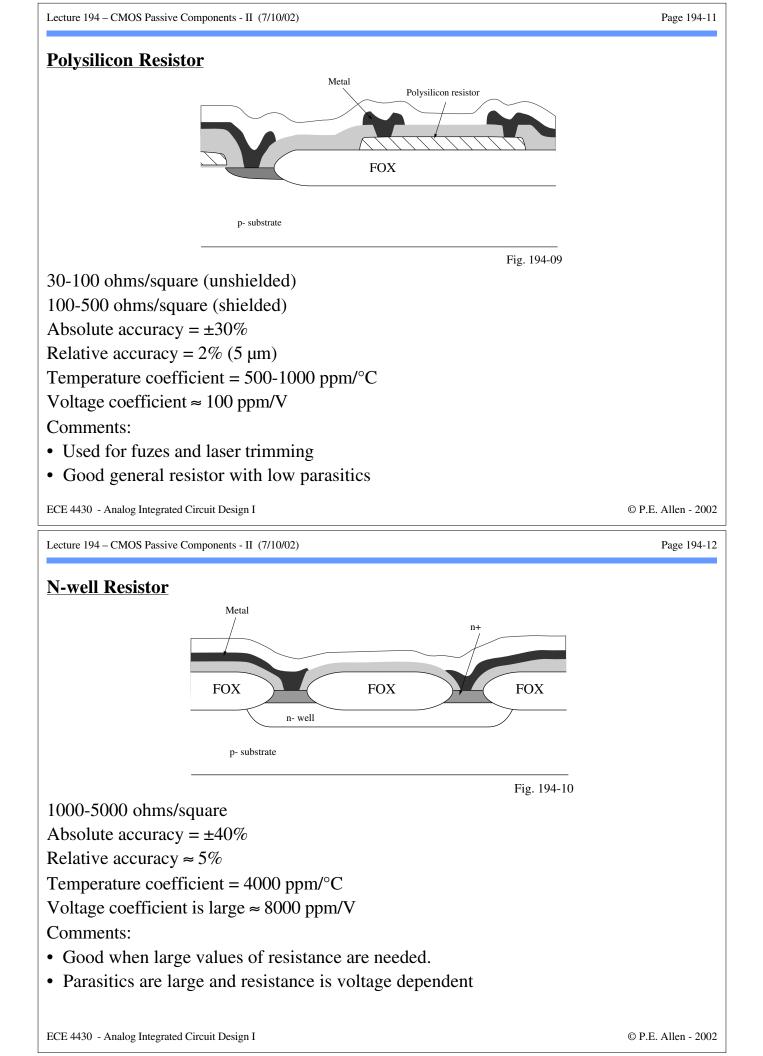

RESISTORS **MOS Resistors - Source/Drain Resistor** Metal SiO. FOX FOX n- well p- substrate Fig. 194-08 Diffusion: Ion Implanted: 10-100 ohms/square 500-2000 ohms/square Absolute accuracy =  $\pm 35\%$ Absolute accuracy =  $\pm 15\%$ Relative accuracy = 2% (5µm), 0.2% (50 Relative accuracy = 2% (5µm), 0.15% μm) (50 µm) Temperature coefficient =  $+1500 \text{ ppm/}^{\circ}\text{C}$ Temperature coefficient =  $+400 \text{ ppm/}^{\circ}\text{C}$ Voltage coefficient  $\approx 200 \text{ ppm/V}$ Voltage coefficient  $\approx 800 \text{ ppm/V}$ Comments: Parasitic capacitance to substrate is voltage dependent.

• Piezoresistance effects occur due to chip strain from mounting.

ECE 4430 - Analog Integrated Circuit Design I

#### **MOS Passive Component Performance Summary**

| Component<br>Type                         | Range of<br>Values         | Absolute<br>Accuracy | Relative<br>Accuracy | Temperature<br>Coefficient | Voltage<br>Coefficient |

|-------------------------------------------|----------------------------|----------------------|----------------------|----------------------------|------------------------|

| Poly-oxide-<br>semiconductor<br>Capacitor | 0.35-0.5<br>fF/µm²         | 10%                  | 0.1%                 | 20ppm/°C                   | ±20ppm/V               |

| Poly-Poly<br>Capacitor                    | 0.3-0.4 fF/µm <sup>2</sup> | 20%                  | 0.1%                 | 25ppm/°C                   | ±50ppm/V               |

| Diffused<br>Resistor                      | 10-100 Ω/sq.               | 35%                  | 2%                   | 1500ppm/°C                 | 200ppm/V               |

| Ion Implanted<br>Resistor                 | 0.5-2 kΩ/sq.               | 15%                  | 2%                   | 400ppm/°C                  | 800ppm/V               |

| Poly Resistor                             | 30-200 Ω/sq.               | 30%                  | 2%                   | 1500ppm/°C                 | 100ppm/V               |

| n-well Resistor                           | 1-10 kΩ/sq.                | 40%                  | 5%                   | 8000ppm/°C                 | 10kppm/V               |

The electrical performance of all passive components greatly depends on the geometry and physical aspects of the layout.

ECE 4430 - Analog Integrated Circuit Design I

Lecture 194 – CMOS Passive Components - II (7/10/02)

**INDUCTORS**

#### **Inductors**

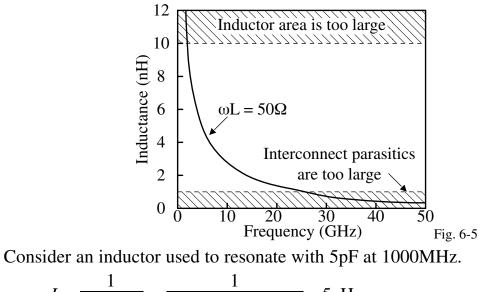

What is the range of values for on-chip inductors?

$$L = \frac{1}{4\pi^2 f_o^2 C} = \frac{1}{(2\pi \cdot 10^9)^2 \cdot 5x \cdot 10^{-12}} = 5\text{nH}$$

Note: Off-chip connections will result in inductance as well.

ECE 4430 - Analog Integrated Circuit Design I

Page 194-14

© P.E. Allen - 2002

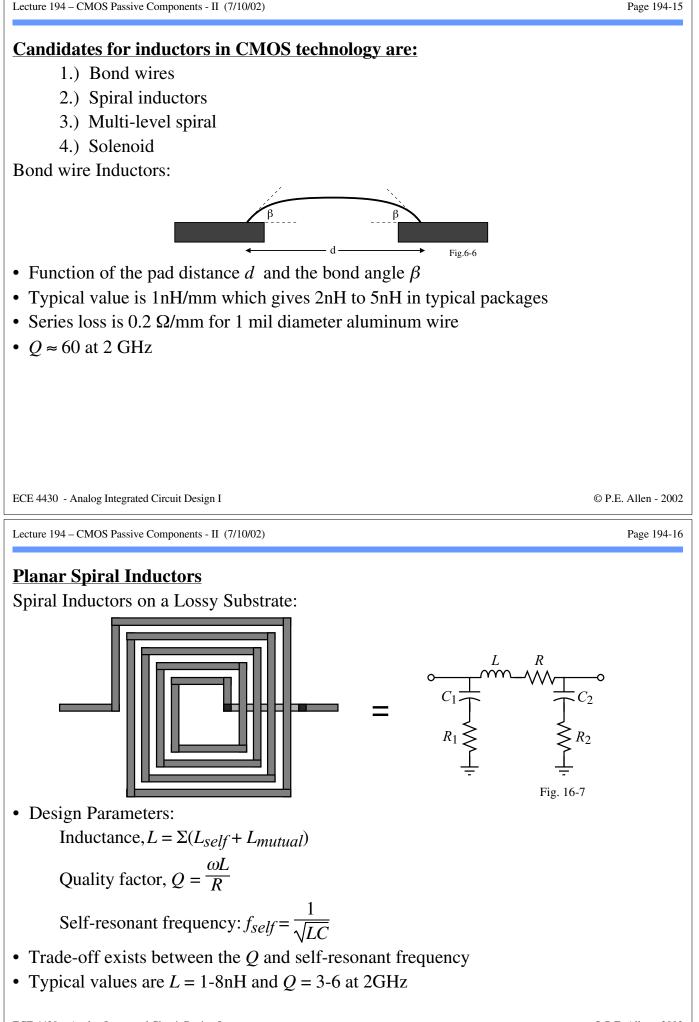

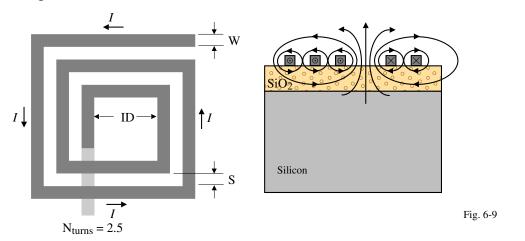

# Planar Spiral Inductors - Continued

Inductor Design

Typically:  $3 < N_{turns} < 5$  and  $S = S_{min}$  for the given current

Select the OD,  $N_{\mbox{turns}},$  and W so that ID allows sufficient magnetic flux to flow through the center.

Loss Mechanisms:

- Skin effect

- Capacitive substrate losses

- Eddy currents in the silicon

ECE 4430 - Analog Integrated Circuit Design I

Lecture 194 – CMOS Passive Components - II (7/10/02)

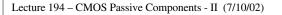

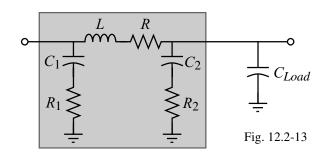

# **Planar Spiral Inductors - Continued**

Influence of a Lossy Substrate

where:

L is the desired inductance

R is the series resistance

$C_1$  and  $C_2$  are the capacitance from the inductor to the ground plane

$R_1$  and  $R_2$  are the eddy current losses in the silicon

Guidelines for using spiral inductors on chip:

- Lossy substrate degrades Q at frequencies close to  $f_{self}$

- To achieve an inductor, one must select frequencies less than  $f_{self}$

- The Q of the capacitors associated with the inductor should be very high

ECE 4430 - Analog Integrated Circuit Design I

© P.E. Allen - 2002

Page 194-18

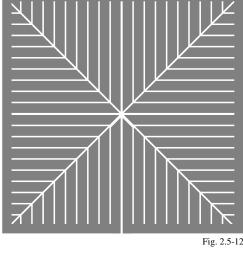

#### **Planar Spiral Inductors - Continued**

Comments concerning implementation:

1.) Put a metal ground shield between the inductor and the silicon to reduce the capacitance.

- Should be patterned so flux goes through but electric field is grounded

- Metal strips should be orthogonal to the spiral to avoid induced loop current

- The resistance of the shield should be low to terminate the electric field

- 2.) Avoid contact resistance wherever possible to keep the series resistance low.

3.) Use the metal with the lowest resistance and furtherest away from the substrate.

4.) Parallel metal strips if other metal levels are available to reduce the resistance.

Example:

© P.E. Allen - 2002

Page 194-20

ECE 4430 - Analog Integrated Circuit Design I

Lecture 194 - CMOS Passive Components - II (7/10/02)

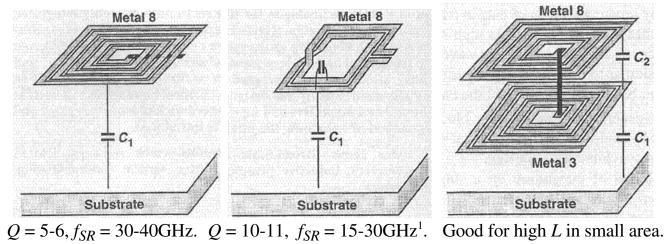

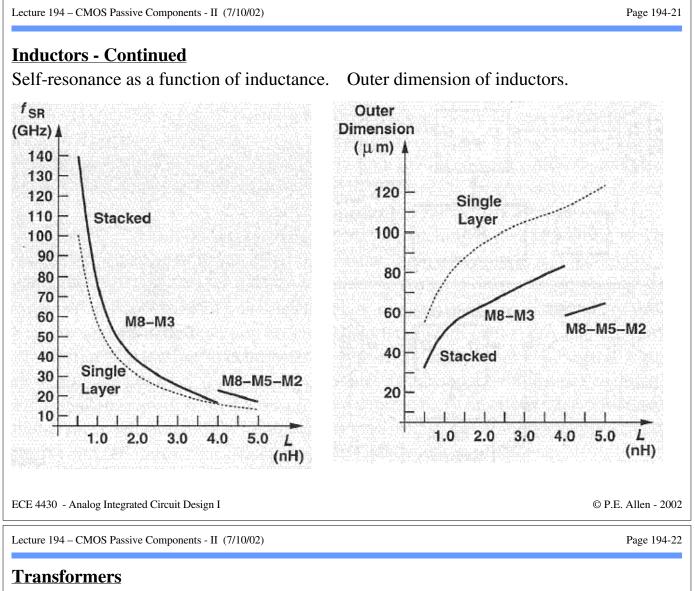

## **Multi-Level Spiral Inductors**

Use of more than one level of metal to make the inductor.

- Can get more inductance per area

- Can increase the interwire capacitance so the different levels are often offset to get minimum overlap.

- Multi-level spiral inductors suffer from contact resistance (must have many parallel contacts to reduce the contact resistance).

- Metal especially designed for inductors is top level approximately 4µm thick.

<sup>1</sup> The skin effect and substrate loss appear to be the limiting factor at higher frequencies of self-resonance. ECE 4430 - Analog Integrated Circuit Design I

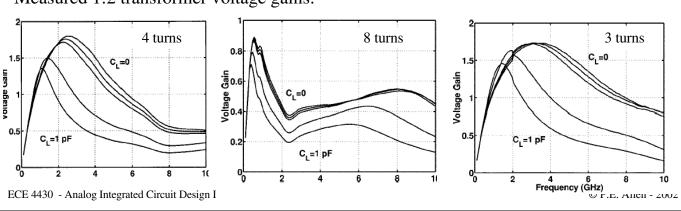

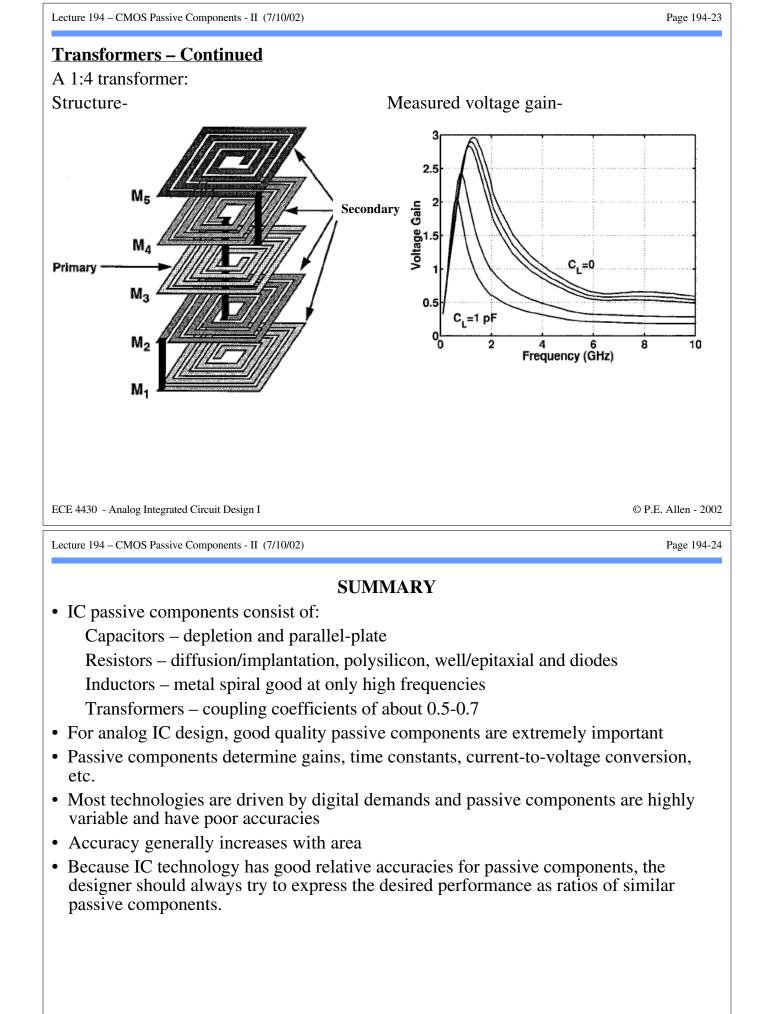

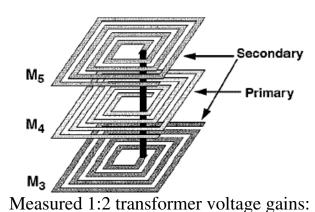

Transformer structures are easily obtained using stacked inductors as shown below for a 1:2 transformer.

Method of reducing the inter-winding capacitances.