# LECTURE 215 – CHAPTER 2 – REVIEW PROBLEMS (READING: Text-Chapter 2)

## **Chapter 2 Topics**

- Integrated Circuit Technology

- Bipolar Technology

- Passive Components in Bipolar Technology

- CMOS Technology

- CMOS Technology-Compatible Devices

- BiCMOS Technology

ECE 4430 - Analog Integrated Circuits and Systems

```

Lecture 215 – Chapter 2 – Review Problems (12/16/01)

```

Page 215-2

© P.E. Allen - 2001

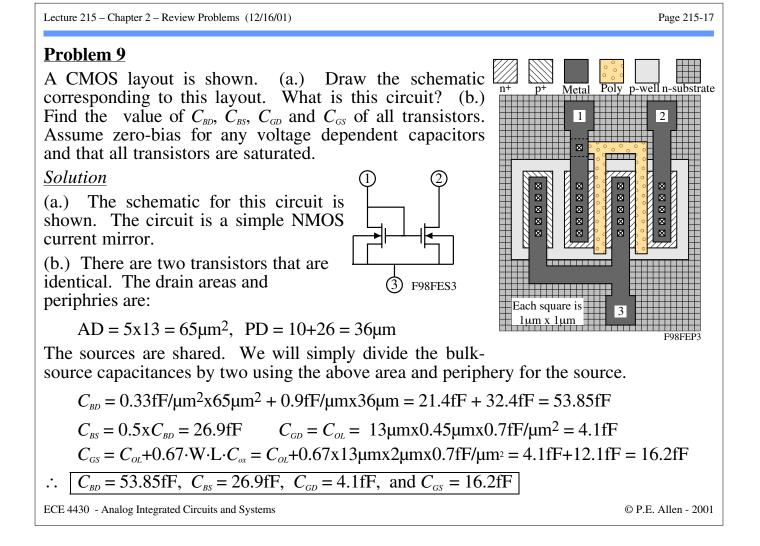

## Problem 1

(a.) Sketch the approximate side view of a NMOS transistor in a p-substrate. Identify each region and identify the connections at the top surface of the integrated circuit for the source, drain, gate and bulk/substrate.

#### <u>Solution</u>

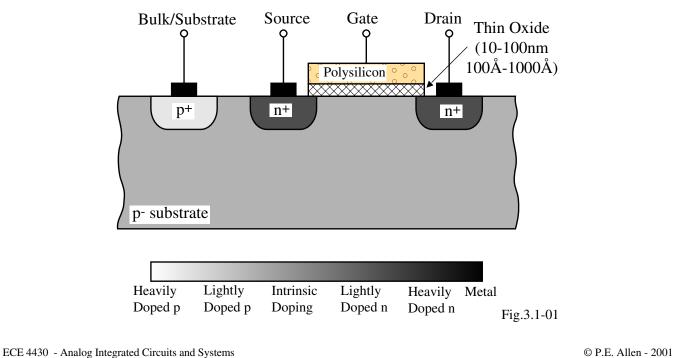

# **Problem 1 - Continued**

(b.) Sketch the approximate side view of a NPN vertical transistor in an n-epitaxial region which is on top of a p-substrate. Identify each region (including the n+ buried layer) and identify the connection at the top surface of the integrated circuit for the base, emitter, collector and substrate.

### Solution

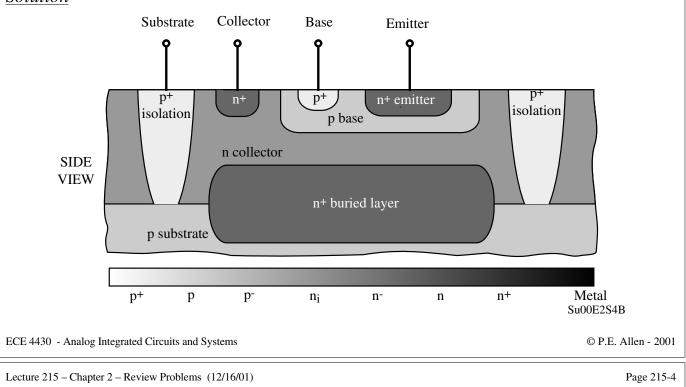

# Problem 2

A layout of a NMOS transistor is shown.

- (a.) Find the values of *RD*, and *RS* in the schematic shown if the sheet resistance of the  $n^+$  is 35  $\Omega$ /sq. and the resistance of a single contact is  $1\Omega$ .

- (b.) Find the values of  $C_{BD}$  and  $C_{BS}$  assuming the transistor is External cutoff and the drain and source are at ground potential if CJ and CJSW for an NMOS transistor are 770x10-6 F/m<sup>2</sup> and 380x10-12F/m. Assume the capacitors are lumped and appear on the source/drain side of the bulk resistors in part (a.).

- (c.) What is the W and L of this transistor?

- Gate Each square is 1µm x 1µm Fig. F00E2P1 (d.) If the overlap capacitor/unit length is  $220 \times 10^{-12}$  F/m, what is  $C_{GD}$ ?

Blue

n+

External

Drain

Gate

$R_D$

Rs

External

Source C

Red

Poly

Х

Black

Metal

External

Drain

Externat

$C_{RD}$

$C_{BS}$

White

Х

Х

Х

White

External

Source

Contact p-substrate

#### **Problem 3**

A simple first-order filter shown is to be built with a polysilicon resistor and a MOS capacitor. The polysilicon resistor has a sheet resistance of  $50\Omega/sq. \pm 30\%$  and is 5µm wide. The MOS capacitor is  $2fF/\mu m^2 \pm 10\%$ . The -3dB frequency of the lowpass filter is 1MHz. (a.) Choose the  $v_{in}$ size of the resistor (the number of squares, N) to minimize the total area of the filter including both the resistor and the capacitor. Find the area of the resistor and the capacitor in  $\mu$ m<sup>2</sup> and their values. (b.) Using the worst-case tolerance of the resistor and capacitor, find the maximum and minimum -3dB frequencies. Solution

(a.) Value of

$$R = 50\Omega/\text{sq.}xN \text{ sq.} = 50N \Omega$$

Value of  $C = 2\text{fF}/\mu\text{m}^2\text{x}A_C\mu\text{m}^2 = 2A_C \text{ fF}$

Area of  $C = A_C$

Area of  $R = A_R = 25\mu\text{m}^2\text{x}N = 25N \mu\text{m}^2$

Total Area  $= A_T = (25N + A_C) \mu\text{m}^2$

We know that the *RC* product is given as

$RC = \frac{1}{2\pi\text{x}10^6} = (50N)(2A_C\text{x}10^{-15}) = NA_C\text{x}10^{-13}$   $\therefore A_C = \frac{1}{2\pi\text{x}10^{-7}N}$

ECE 4430 - Analog Integrated Circuits and Systems

*R<sub>voly</sub>*

CMOS

vout

F00E2P2

Lecture 215 – Chapter 2 – Review Problems (12/16/01)

**Problem 3 - Continued**

Thus,  $A_T = 25N + \frac{1}{2\pi x 10^{-7}N} \rightarrow \frac{dA_T}{dN} = 25 - \frac{1}{2\pi x 10^{-7}N^2} = 0$   $\therefore N = \frac{1}{\sqrt{50\pi x 10^{-7}}} = 252 \Rightarrow A_{\underline{R}} = 252x25\mu m^2 = 6308\mu m^2 \text{ and } A_{\underline{C}} = 6308\mu m^2$ Also,  $R_{\underline{poly}} = R = 252x50\Omega = 12.6k\Omega$  and  $C_{\underline{MOS}} = 6308\mu m^2 x 2fF/\mu m^2 = 12.6pF$ (b.) Maximum -3dB frequency  $= \frac{1}{2\pi (0.7)(12.6k\Omega)(0.9)(12.6pF)} = 1.6MHz$ Minimum -3dB frequency  $= \frac{1}{2\pi (1.3)(12.6k\Omega)(1.1)(12.6pF)} = 0.7MHz$

ECE 4430 - Analog Integrated Circuits and Systems

© P.E. Allen - 2001

Page 215-8

Lecture 215 – Chapter 2 – Review Problems (12/16/01)

#### Problem 4

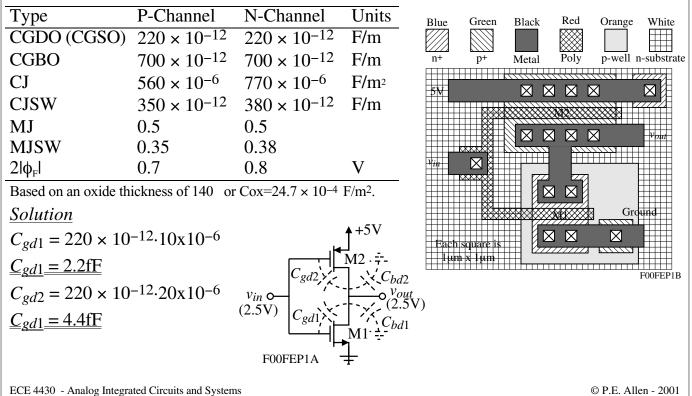

A CMOS amplifier is shown along with the top view of the circuit layout assuming a pwell CMOS technology. Find the values of the capacitors shown in the circuit if

## **Problem 4 - Continued**

Next, we must find the area and perimeter of each drain.

AD1 = 60µm<sup>2</sup> & PD1 = 32µm

AD2 = 120µm<sup>2</sup> & PD2 = 52µm

$$C_{bd1} = \frac{\text{CJ} \cdot \text{AD1}}{\left[1 + \frac{2.5V}{2|\phi_{\text{FI}}|}\right]\text{MJ}} + \frac{\text{CJSW} \cdot \text{PD1}}{\left(1 + \frac{2.5V}{2|\phi_{\text{FI}}|}\right]\text{MJSW}} = \frac{770 \times 10^{-6} \cdot 60 \times 10^{-12}}{\left(1 + \frac{2.5V}{0.8}\right]^{0.5}} + \frac{380 \times 10^{-12} \cdot 32 \times 10^{-6}}{\left(1 + \frac{2.5V}{0.8}\right]^{0.38}}$$

$$\frac{C_{bd1} = 22.75\text{ FF} + 7.10\text{ FF} = 29.84\text{ FF}}{C_{bd2}} = \frac{\text{CJ} \cdot \text{AD2}}{\left(1 + \frac{2.5V}{2|\phi_{\text{FI}}|}\right)\text{MJ}} + \frac{\text{CJSW} \cdot \text{PD2}}{\left(1 + \frac{2.5V}{2.0\varphi_{\text{FI}}}\right)^{0.5}} = \frac{560 \times 10^{-6} \cdot 120 \times 10^{-12}}{\left(1 + \frac{2.5V}{0.7}\right)^{0.5}} + \frac{350 \times 10^{-12} \cdot 52 \times 10^{-6}}{\left(1 + \frac{2.5V}{0.7}\right)^{0.35}}$$

$$C_{bd2} = \frac{\text{CJ} \cdot \text{AD2}}{\left(1 + \frac{2.5V}{2|\phi_{\text{FI}}|}\right)\text{MJ}} + \frac{\text{CJSW} \cdot \text{PD2}}{\left(1 + \frac{2.5V}{2.0\varphi_{\text{FI}}}\right)^{0.5}} = \frac{560 \times 10^{-6} \cdot 120 \times 10^{-12}}{\left(1 + \frac{2.5V}{0.7}\right)^{0.35}} + \frac{350 \times 10^{-12} \cdot 52 \times 10^{-6}}{\left(1 + \frac{2.5V}{0.7}\right)^{0.35}}$$

$$C_{bd2} = 31.43\text{ fF} + 10.69\text{ fF} = 42.12\text{ fF}$$

ECE 4430 - Analog Integrated Circuits and Systems

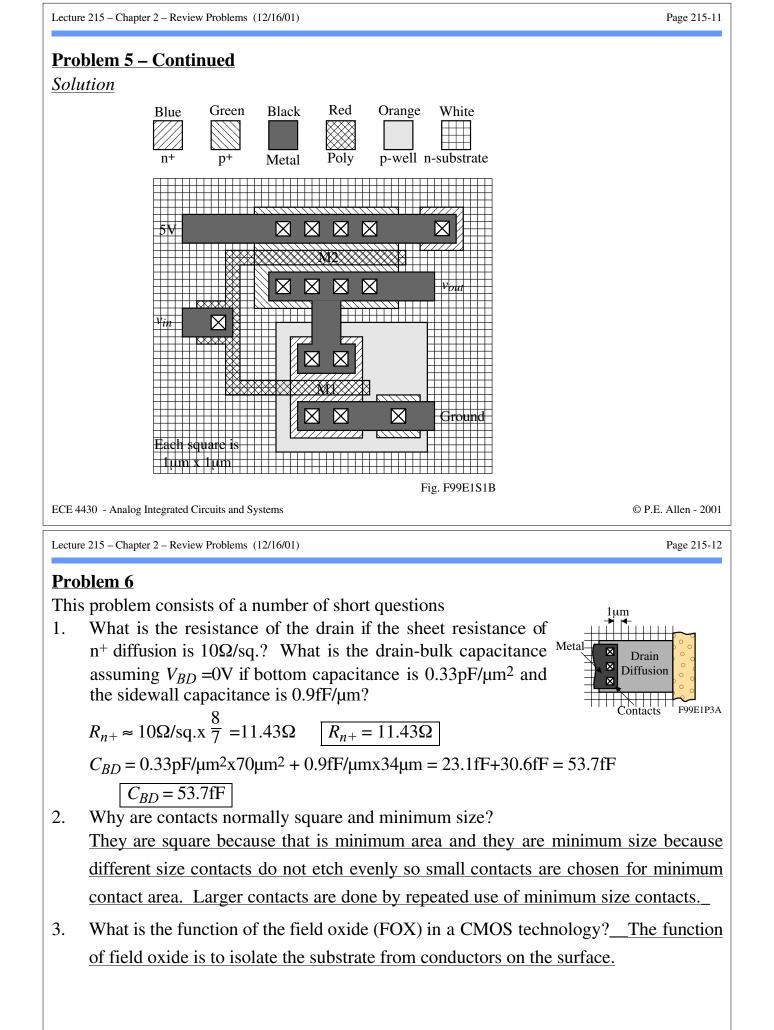

$$Problem 5$$

A CMOS circuit is shown. Assume a p-well CMOS technology and draw the complete layout for the NMOS and PMOS transistors that  $\mathbf{A} + 5V$

draw the complete layout for the NMOS and PMOS transistors that has *minimum* rectangular area for the source and drain diffusions. Some pertinent design rules are listed below.

- DR1 = distance from the square contact to diffusion from polysilicon = 2µm

- DR2 = all contacts are to be square with a dimension of  $2\mu m$  by  $2\mu m$

- DR3 = the overlap of the contact by the diffusion or  $poly = 2\mu m$

- DR4 = min. separation between  $n^+$  diffusion and p-well =  $2\mu m$

- DR5 = minimum overlap of contact by metal =  $1\mu m$

- $DR6 = poly must overlap the channel by 1 \mu m$

All metal widths are to be  $4\mu m$ . Put as many contacts between the metal and diffusions as possible. Show the metal connections between transistors and indicate where metal goes for connections from transistors to external connections ( $v_{in}$  and  $v_{out}$  must be in metal). Use the indicated scheme below for identifying the various regions. If you wish to use colored pencil, use the scheme below or indicate which colors pertain to which region.

20um

2µm

$o V_{out}$

10um

2µm

F99E1P1A

M1

# **Problem 6 – Continued**

4. How are two BJT transistors fabricated in the same substrate electrically isolated from each other? Each BJT is fabricated in its own n-epitaxial region surrounded on all sides by p material. This pn junction is reversed biased to electrically isolate the two transistors.

5. Assume that a 1kΩ resistance of an IC process has a voltage coefficient of -1000ppm/V. What is the resistance value if the average voltage across the resistor is increased from 0 to 5V?

$R(5V) = R(0V) - \frac{1000}{1,000,000} 5Vx1000\Omega = 1000\Omega - 5\Omega = 995\Omega \quad \boxed{R(5V) = 995\Omega}$

- 6. List the 5 capacitances associated with the MOSFET operating in the saturation region and tell whether this capacitance is depletion or parallel plate or both.

- 1.) Gate -drain which is parallel plate\_

- 2.) Gate-source which is both parallel plate and depletion\_

- 3.) Bulk-drain which is depletion

- 4.) Bulk-source which is depletion

- 5.) Gate-bulk which is parallel plate\_

ECE 4430 - Analog Integrated Circuits and Systems

© P.E. Allen - 2001

Page 215-14

Lecture 215 – Chapter 2 – Review Problems (12/16/01)

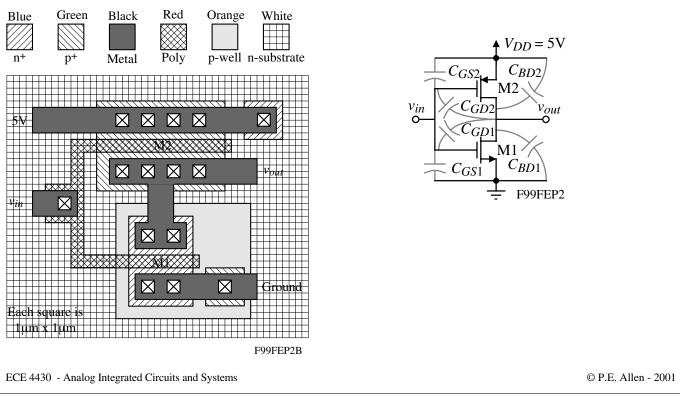

# Problem 7

A top view of a CMOS push-pull amplifier is shown. Find the numerical value of all capacitances shown on the schematic. Assume that the dc value of the output is 2.5V and the MJ and MJSW is 0.5 for both transistors.

## **Problem 7 - Continued**

41:

$$W_{1} = 10\mu\text{m}, L_{1} = 2\mu\text{m}, AS_{1} = AD_{1} = 6x10 = 60\mu\text{m}^{2}, PS_{1} = PD_{1} = 32\mu\text{m}$$

$$C_{GD1} = 10\mu\text{m}\cdot0.45\mu\text{m}\cdot0.7\text{fF}/\mu\text{m}^{2} = 3\underline{.15\text{fF}}$$

$$C_{BD1} = \frac{[60\mu\text{m}^{2}\cdot0.33\text{fF}/\text{m}^{2}+32\mu\text{m}\cdot0.9\text{fF}/\mu\text{m}]}{\sqrt{1+\frac{2.5}{0.6}}} = \underline{21.38\text{fF}}$$

$$C_{GS1} = 10\mu\text{m}\cdot0.45\mu\text{m}\cdot0.7\text{fF}/\mu\text{m}^{2} + 0.67[20\mu\text{m}^{2}\cdot0.7\text{fF}/\text{m}^{2}] = \underline{12.48\text{fF}}$$

M2:

$$\begin{split} W_2 &= 20 \mu \text{m}, L_2 = 2 \mu \text{m}, AS_2 = AD_2 = 6 \text{x} 20 = 120 \mu \text{m}^2, PS_2 = PD_2 = 52 \mu \text{m}^2, \\ C_{GD2} &= 20 \mu \text{m} \cdot 0.6 \mu \text{m} \cdot 0.7 \text{fF} / \mu \text{m}^2 = 8 \underline{.4 \text{fF}} \\ C_{BD2} &= \frac{[120 \mu \text{m}^2 \cdot 0.38 \text{fF} / \text{m}^2 + 52 \mu \text{m} \cdot 1 \text{fF} / \mu \text{m}]}{\sqrt{1 + \frac{2.5}{0.6}}} = \underline{42.94 \text{fF}} \\ C_{GS2} &= 20 \mu \text{m} \cdot 0.6 \mu \text{m} \cdot 0.7 \text{fF} / \mu \text{m}^2 + 0.67 [40 \mu \text{m}^2 \cdot 0.7 \text{fF} / \text{m}^2] = \underline{27 \text{fF}} \end{split}$$

ECE 4430 - Analog Integrated Circuits and Systems

Lecture 215 – Chapter 2 – Review Problems (12/16/01)

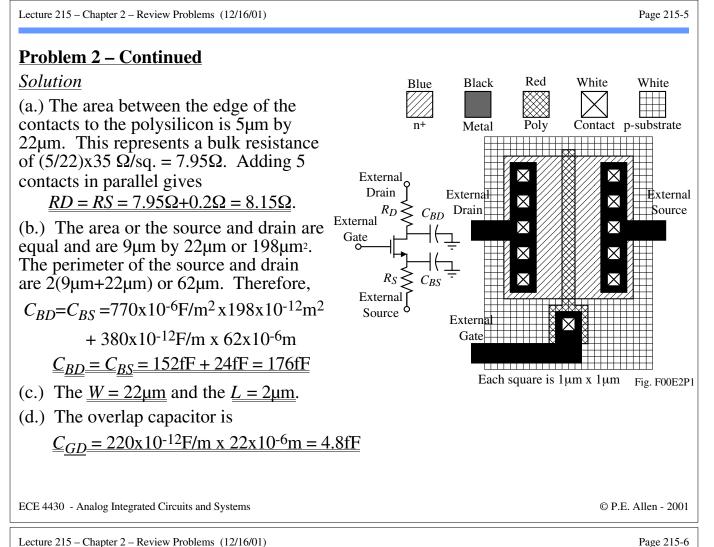

# **Problem 8**

This problem consists of a number of short questions

List three functions of polysilicon. 1.

(1) Gate of a MOS transistor

- (2) Ohmic connection between two points

- (3) Resistor

- (4) Capacitor plate

- In a CMOS technology, list three functions for the n<sup>+</sup> or p<sup>+</sup> diffusions. 2.

- (1) They can form the source or drain of a MOSFET

- (2) They are used to make an ohmic contact with metal

- (3)\_\_\_\_They can be used as a resistor\_\_\_\_\_

- (4) Capacitor plate

- Nitride is only used to define the active areas of transistors. True\_\_\_\_ or False\_X\_ 3.

- How are two NMOS transistors fabricated in the same substrate electrically 4. isolated from each other?

They are fabricated in an oppositely doped substrate so that they can be reverse biased and thus isolated from the substrate and from each other.

5. What is the purpose of masks in an integrated circuit fabrication process? To allow selective processing of an area of a wafer.

© P.E. Allen - 2001

Page 215-16