## **Objective**

The objective of this presentation is:

1.) Illustrate the performance and design of a two-stage open-loop comparator

# **Outline**

- Two-stage, open-loop comparator performance

- Initial states of the two-stage, open-loop comparator

- Propagation delay time of a slewing, two-stage, open-loop comparator

- Design of a two-stage, open-loop comparator

- Summary

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002

Page 370-2

Lecture 370 – Two-Stage Open-Loop Comparators-I (4/5/02)

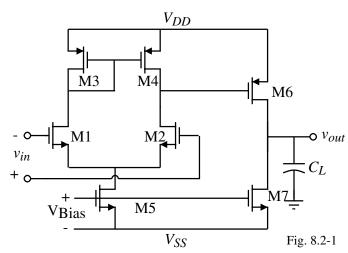

## **Two-Stage Comparator**

An important category of comparators are those which use a high-gain stage to drive their outputs between  $V_{OH}$  and  $V_{OL}$  for very small input voltage changes.

The two-stage op amp without compensation is an excellent implementation of a highgain, open-loop comparator.

We know the performance should be similar to the uncompensated two-stage op amp. Emphasis on comparator performance:

• Maximum output voltage

$$V_{OH} = V_{DD} - (V_{DD} - V_{G6}(\min) - |V_{TP}|) \left[ 1 - \sqrt{1 - \frac{8I_7}{\beta_6 (V_{DD} - V_{G6}(\min) - |V_{TP}|)^2}} \right]$$

Output:

$p_2 = \frac{-(g_{ds6} + g_{ds7})}{C_{II}}$

• Minimum output voltage

$$V_{OL} = V_{SS}$$

• Small-signal voltage gain

$$A_{\mathcal{V}}(0) = \left(\frac{g_{m1}}{g_{ds2} + g_{ds4}}\right) \left(\frac{g_{m6}}{g_{ds6} + g_{ds7}}\right)$$

• Poles

Input:

$$p_1 = \frac{-(g_{ds2} + g_{ds4})}{C_I}$$

• Frequency response

$$A_{\nu}(s) = \frac{A_{\nu}(0)}{\left(\frac{s}{p_1} + 1\right)\left(\frac{s}{p_2} + 1\right)}$$

ECE 6412 - Analog Integrated Circuit Design - II

Lecture 370 – Two-Stage Open-Loop Comparators-I (4/5/02)

## **Example 2-1 - Performance of a Two-Stage Comparator**

Evaluate  $V_{OH}$ ,  $V_{OL}$ ,  $A_v(0)$ ,  $V_{in}(\min)$ ,  $p_1$ ,  $p_2$ , for the two-stage comparator in Fig. 8.2-1. Assume that this comparator is the circuit of Ex. 6.3-1 with no compensation capacitor,  $C_c$ , and the minimum value of  $V_{G6} = 0$ V. Also, assume that  $C_I = 0.2$  pF and  $C_{II} = 5$  pF. Solution

Using the above relations, we find that

$$V_{OH} = 2.5 - (2.5 - 0.7) \left[ 1 - \sqrt{1 - \frac{8 \cdot 234 \times 10^{-6}}{50 \times 10^{-6} \cdot 38(2.5 - 0.7)^2}} \right] = 2.2 \text{V}$$

The value of  $V_{OL}$  is -2.5V. The gain was evaluated in Ex. 6.3-1 as  $A_v(0) = 7696$ . Therefore, the input resolution is

$$V_{in}(\min) = \frac{V_{OH} - V_{OL}}{A_v(0)} = \frac{4.7 \text{V}}{7696} = 0.611 \text{mV}$$

Next, we find the poles of the comparator,  $p_1$  and  $p_2$ . From Ex. 6.3-1 we find that

$$p_1 = \frac{g_{ds2} + g_{ds4}}{C_I} = \frac{15x10^{-6}(0.04 + 0.05)}{0.2x10^{-12}} = 6.75x10^6 (1.074 \text{MHz})$$

and

$$p_2 = \frac{g_{ds6} + g_{ds7}}{C_{II}} = \frac{95 \times 10^{-6} (0.04 + 0.05)}{5 \times 10^{-12}} = 1.71 \times 10^{6} (0.272 \text{MHz})$$

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002

Page 370-4

© P.E. Allen - 2002

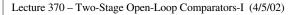

The step response of a circuit with two real poles  $(p_1 \neq p_2)$  is,

$$v_{out}(t) = A_v(0)V_{in}\left[1 + \frac{p_2 e^{-tp_1}}{p_1 - p_2} - \frac{p_1 e^{-tp_2}}{p_1 - p_2}\right]$$

Normalizing gives,

$$v_{out}'(t_n) = \frac{v_{out}(t)}{A_v(0)V_{in}} = 1 - \frac{m}{m-1}e^{-t_n} + \frac{1}{m-1}e^{-mt_n}$$

where  $m = \frac{p_2}{p_1} \neq 1$  and  $t_n = tp_1 = \frac{t}{\tau_1}$

If  $p_1 = p_2$  ( $m = 1$ ), then  $v_{out}'(t_n) = 1 - p_1e^{-t_n} - \frac{t_n}{p_1}e^{-t_n} = 1 - e^{-t_n} - t_ne^{-t_n}$  where  $p_1 = 1$ .

$$ECE 6412 - Analog Integrated Circuit Design - II

$$m = 4$$

$$m = 0.5$$

$$m = 0.25$$

$$m = 0.25$$

$$m = 0.25$$

$$m = 0.25$$

$$m = \frac{p_2}{p_1}$$

$$m = \frac{p_2}{p_2}$$

$$m = \frac{p_2}{p_1}$$

$$m = \frac{p_2}{p_2}$$

$$m =$$$$

Lecture 370 - Two-Stage Open-Loop Comparators-I (4/5/02)

#### Page 370-6

#### Linear Step Response of the Two-Stage Comparator - Continued

The above results are valid as long as the slope of the linear response does not exceed the slew rate.

- Slope at t = 0 is zero

- Maximum slope occurs at  $(m \neq 1)$

$$t_n(\max) = \frac{ln(m)}{m-1}$$

and is

$$\frac{dv_{out}'(t_n(\max))}{dt_n} = \frac{m}{m-1} \left[ \exp\left(\frac{-ln(m)}{m-1}\right) - \exp\left(-m\frac{ln(m)}{m-1}\right) \right]$$

• For the two-stage comparator using NMOS input transistors, the slew rate is

$$SR^{-} = \frac{I_{7}}{C_{II}}$$

$$SR^{+} = \frac{I_{6} - I_{7}}{C_{II}} = \frac{0.5\beta_{6}(V_{DD} - V_{G6}(\min) - |V_{TP}|)^{2} - I_{7}}{C_{II}}$$

Lecture 370 - Two-Stage Open-Loop Comparators-I (4/5/02)

#### Example 2-2 - Step Response of Ex. 2-1

Find the maximum slope of Ex. 2-1 and the time at which it occurs if the magnitude of the input step is  $v_{in}(\min)$ . If the dc bias current in M7 is 100µA, at what value of load capacitance,  $C_L$  would the transient response become slew limited? If the magnitude of the input step is  $100v_{in}(\min)$ , what is the new value of  $C_L$  at which slewing would occur? <u>Solution</u>

The poles of the comparator were given in Ex. 2-1 as  $p_1 = -6.75 \times 10^6$  rads/sec. and  $p_2 = -1.71 \times 10^6$  rads/sec. This gives a value of m = 0.253. From the previous expressions, the maximum slope occurs at  $t_n(\max) = 1.84$  secs. Dividing by  $|p_1|$  gives  $t(\max) = 0.272 \mu$ s. The slope of the transient response at this time is found as

$$\frac{dv_{out}'(t_n(\max))}{dt_n} = -0.338[\exp(-1.84) - \exp(-0.253 \cdot 1.84)] = 0.159 \text{ V/sec}$$

Multiplying the above by  $|p_1|$  gives

$$\frac{dv_{out}'(t(\max))}{dt} = 1.072 \text{V/}\mu\text{s}$$

Therefore, if the slew rate is less than 1.072V/µs, the transient response will experience slewing. Also, if  $C_L \ge 100\mu A/1.072V/\mu s$  or 93.3pF, the comparator will slew.

If the input is  $100v_{in}(\min)$ , then we must unnormalize the output slope as follows.

$$\frac{dv_{out}'(t(\max))}{dt} = \frac{v_{in}}{v_{in}(\min)} \frac{dv_{out}'(t(\max))}{dt} = 100.1.072 \text{V/}\mu\text{s} = 107.2 \text{V/}\mu\text{s}$$

Therefore, the comparator will now slew with a load capacitance of 0.933pF.

ECE 6412 - Analog Integrated Circuit Design - II

Lecture 370 – Two-Stage Open-Loop Comparators-I (4/5/02)

## **Propagation Delay Time (Non-Slew)**

To find  $t_p$ , we want to set  $0.5(V_{OH}-V_{OL})$  equal to  $v_{out}(t_n)$ . However,  $v_{out}(t_n)$  given as

$$v_{out}(t_n) = A_v(0)V_{in}\left[1 - \frac{m}{m-1}e^{-t_n} + \frac{1}{m-1}e^{-mt_n}\right]$$

can't be easily solved so approximate the step response as a power series to get

$$v_{out}(t_n) \approx A_v(0) V_{in} \left[ 1 - \frac{m}{m-1} \left( 1 - t_n + \frac{t_n^2}{2} + \cdots \right) + \frac{1}{m-1} \left( 1 - mt_n + \frac{m^2 t_n^2}{2} + \cdots \right) \right] \approx \frac{mt_n^2 A_v(0) V_{in}}{2}$$

Therefore, set  $v_{out}(t_n) = 0.5(V_{OH}-V_{OL})$

$$\frac{V_{OH}+V_{OL}}{2} \approx \frac{mt_{pn}^2 A_v(0) V_{in}}{2}$$

or

$$t_{pn} \approx \sqrt{\frac{V_{OH} + V_{OL}}{mA_v(0)V_{in}}} = \sqrt{\frac{V_{in}(\min)}{mV_{in}}} = \frac{1}{\sqrt{mk}}$$

This approximation is particularly good for large values of *k*.

© P.E. Allen - 2002

Page 370-8

# **Example 2-3 - Propagation Delay Time of a Two-Pole Comparator (Non-Slew)**

Find the propagation time delay of Ex. 2-1 if  $V_{in} = 10$ mV, 100mV and 1V.

### <u>Solution</u>

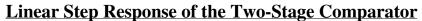

1.) Assume  $v_{G2} = V_{REF}$  and  $v_{G1} > V_{REF}$ with  $i_1 < I_{SS}$  and  $i_2 > 0$ .

Initially,  $i_4 > i_2$  and  $v_{o1}$  increases, M4 becomes active and  $i_4$  decreases until  $i_3 = i_4$ .  $v_{o1}$  is in the range of,

$$V_{DD} - V_{SD4}(\text{sat}) < v_{01} < V_{DD},$$

$v_{G1} > V_{REF}, i_1 < I_{SS} \text{ and } i_2 > 0$

$v_{G1} > V_{REF}$ ,  $i_1 < I_{SS}$  and  $i_2 > 0$

VBias

Iss

M5

VSS

and the value of vout is

$v_{out} \approx V_{SS}$

2.) Assume  $v_{G2} = V_{REF}$  and  $v_{G1} >> V_{REF}$ , therefore  $i_1 = I_{SS}$  and  $i_2 = 0$  which gives  $v_{o1} = V_{DD}$  and  $v_{out} = V_{SS}$

ECE 6412 - Analog Integrated Circuit Design - II

Cп

Fig. 8.2-3

#### **Initial Operating States - Continued**

3.) Assume  $v_{G2} = V_{REF}$  and  $v_{G1} < V_{REF}$  with  $i_1 > 0$  and  $i_2 < I_{SS}$ .

Initially,  $i_4 < i_2$  and  $v_{o1}$  decreases. When  $v_{o1} \le V_{REF} - V_{TN}$ , M2 becomes active and  $i_2$  decreases. When  $i_1 = i_2 = I_{SS}/2$  the circuit stabilizes and  $v_{o1}$  is in the range of,

$$V_{REF} - V_{GS2} < v_{o1} < V_{REF} - V_{GS2} + V_{DS2}$$

(sat)

or

$$V_{S2} < v_{o1} < V_{S2} + V_{DS2}(\text{sat}),$$

$$v_{G1} < V_{G2}, i_1 > 0 \text{ and } i_2 < I_{SS}$$

For the above conditions,

$$v_{out} = V_{DD} - (V_{DD} - v_{o1} - |V_{TP}|) \left[ 1 - \sqrt{1 - \frac{\beta_7 I_{SS}}{\beta_5 \beta_6 (V_{DD} - v_{o1} - |V_{TP}|)^2}} \right]$$

4.) Assume  $v_{G2} = V_{REF}$  and  $v_{G1} \ll V_{REF}$ , therefore  $i_2 = I_{SS}$  and  $i_1 = 0$ .

Same as in 3.) but now as  $v_{o1}$  approaches  $v_{S2}$  with  $I_{SS}/2$  flowing, the value of  $v_{GS2}$  becomes larger and M5 becomes active and  $I_{SS}$  decreases. In the limit,  $I_{SS} \rightarrow 0, v_{DS2} \approx 0$  and  $v_{DS5} \approx 0$  resulting in

$$v_{o1} \approx V_{SS}$$

and  $v_{out} = V_{DD} - (V_{DD} - V_{SS})$

$|V_{TP}| \left[ 1 - \sqrt{1 - \frac{\beta_7 I_{SS}}{\beta_5 \beta_6 (V_{DD} - V_{SS} - |V_{TP}|)^2}} \right]$

ECE 6412 - Analog Integrated Circuit Design - II

Lecture 370 – Two-Stage Open-Loop Comparators-I (4/5/02)

#### **Initial Operating States - Continued**

5.) Assume  $v_{G1} = V_{REF}$  and  $v_{G2} > V_{REF}$  with  $i_2 < I_{SS}$  and  $i_1 > 0$ .

Initially,  $i_4 < i_2$  and  $v_{o1}$  falls, M2 becomes active and  $i_2$  decreases until  $i_1 = i_2 = I_{SS}/2$ . Therefore,

$$V_{REF} - V_{GS2}(I_{SS}/2) < v_{o1} < V_{REF} - V_{GS2}(I_{SS}/2) + V_{DS2}(sat)$$

or

$V_{S2}(I_{SS}/2) < v_{o1} < V_{S2}(I_{SS}/2) + V_{DS2}(\text{sat}), \quad v_{G2} > V_{REF}, i_1 > 0 \text{ and } i_2 < I_{SS}$ and the value of  $v_{out}$  is

$$v_{out} = V_{DD} - (V_{DD} - v_{o1} - |V_{TP}|) \left[ 1 - \sqrt{1 - \frac{\beta_7 I_{SS}}{\beta_5 \beta_6 (V_{DD} - v_{o1} - |V_{TP}|)^2}} \right]$$

6.) Assume that  $v_{G1} = V_{REF}$  and  $v_{G2} >> V_{REF}$ . When the source voltage of M1 or M2 causes M5 to be active, then  $I_{SS}$  decreases and

$$v_{o1} \approx V_{SS}$$

and  $v_{out} = V_{DD} - (V_{DD} - V_{SS} - |V_{TP}|) \left[ 1 - \sqrt{1 - \frac{\beta_7 I_{SS}}{\beta_5 \beta_6 (V_{DD} - V_{SS} - |V_{TP}|)^2}} \right]$

Г

7.) Assume  $v_{G1} = V_{REF}$  and  $v_{G2} < V_{REF}$  and  $i_1 < I_{SS}$  and  $i_2 > 0$ . Consequently,  $i_4 > i_2$  which causes  $v_{o1}$  to increase. When M4 becomes active  $i_4$  decreases until  $i_2 = i_4$  at which  $v_{o1}$  stabilizes at (M6 will be off under these conditions and  $v_{out} \approx V_{SS}$ ).

$$V_{DD} - V_{SD4}(\text{sat}) < v_{o1} < V_{DD},$$

$v_{G2} < V_{REF}, i_1 < I_{SS} \text{ and } i_2 > 0$

© P.E. Allen - 2002

Page 370-12

Lecture 370 – Two-Stage Open-Loop Comparators-I (4/5/02)

## **Initial Operating States - Continued**

8.) Finally if  $v_{G2} \ll V_{REF}$ , then  $i_1 = I_{SS}$  and  $i_2 = 0$  and

$$v_{o1} \approx V_{DD}$$

and  $v_{out} \approx V_{SS}$ .

Summary of the Initial Operating States of the Two-Stage, Open-Loop Comparator using a N-channel, Source-coupled Input Pair:

| Conditions                                                        | Initial State of $v_{01}$                                               | Initial State of <i>v<sub>out</sub></i> |

|-------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------|

| $v_{G1} > V_{G2}, i_1 < I_{SS} \text{ and } i_2 > 0$              | $V_{DD}$ - $V_{SD4}(sat) < v_{o1} < V_{DD}$                             | V <sub>SS</sub>                         |

| $v_{G1} >> V_{G2}, i_1 = I_{SS} \text{ and } i_2 = 0$             | $V_{DD}$                                                                | $V_{SS}$                                |

| $v_{G1} < V_{G2}, i_1 > 0$ and $i_2 < I_{SS}$                     | $v_{O1} = V_{G2} - V_{GS2,act}(I_{SS}/2), \approx V_{SS}$ if M5<br>act. | Eq. (19), Sec. 5.1 for PMOS             |

| $v_{G1} \ll V_{G2}, i_1 \gg 0$ and $i_2 \ll I_{SS}$               | $V_{SS}$                                                                | Eq. (19), Sec. 5.1 for PMOS             |

| $v_{G2} > V_{G1}, i_1 > 0 \text{ and } i_2 < I_{SS}$              | $V_{S2}(I_{SS}/2) < v_{o1} < V_{S2}(I_{SS}/2) + V_{DS2}(sat)$           | Eq. (19), Sec. 5.1 for PMOS             |

| $v_{G2} >> V_{G1}, i_1 >0 \text{ and } i_2 < I_{SS}$              | $V_{G1}-V_{GS1}(I_{SS}/2)$ , $\approx V_{SS}$ if M5 active              | Eq. (19), Sec. 5.1 for PMOS             |

| <i>vG</i> 2< <i>VG</i> 1, <i>i</i> 1< <i>ISS</i> and <i>i</i> 2>0 | $V_{DD}$ - $V_{SD4}(sat) < v_{O1} < V_{DD}$                             | $V_{SS}$                                |

| $v_{G2} << V_{G1}, i_1 = I_{SS} \text{ and } i_2 = 0$             | $V_{DD}$                                                                | $V_{SS}$                                |

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002

Page 370-14

Lecture 370 - Two-Stage Open-Loop Comparators-I (4/5/02)

# **TO BE CONTINUED IN THE NEXT LECTURE**