# LECTURE 120 – COMPENSATION OF OP AMPS - I (READING: GHLM – 624-638, AH – 249-260)

#### INTRODUCTION

The objective of this presentation is to present the principles of compensating two-stage op amps.

#### **Outline**

- Compensation of Op Amps

General principles

Miller, Nulling Miller

Self-compensation

Feedforward

- Summary

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002

Lecture 120 – Compensation of Op Amps-I (1/26/04)

Page 120-2

#### GENERAL PRINCIPLES OF OP AMP COMPENSATION

## **Objective**

Objective of compensation is to achieve stable operation when negative feedback is applied around the op amp.

## **Types of Compensation**

- 1. Miller Use of a capacitor feeding back around a high-gain, inverting stage.

- Miller capacitor only

- Miller capacitor with an unity-gain buffer to block the forward path through the compensation capacitor. Can eliminate the RHP zero.

- Miller with a nulling resistor. Similar to Miller but with an added series resistance to gain control over the RHP zero.

- 2. Feedforward Bypassing a positive gain amplifier resulting in phase lead. Gain can be less than unity.

- 3. Self compensating Load capacitor compensates the op amp.

## Single-Loop, Negative Feedback Systems

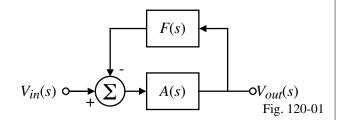

Block diagram:

A(s) = differential-mode voltage gain of the op amp

F(s) = feedback transfer function from the output of op amp back to the input.

#### **Definitions:**

• Open-loop gain = L(s) = -A(s)F(s)

• Closed-loop gain =

$$\frac{V_{out}(s)}{V_{in}(s)} = \frac{A(s)}{1 + A(s)F(s)}$$

**Stability Requirements:**

The requirements for stability for a single-loop, negative feedback system is,

$$|A(j\omega_0^\circ)F(j\omega_0^\circ)| = |L(j\omega_0^\circ)| < 1$$

where  $\omega_{0}$ ° is defined as

$$\operatorname{Arg}[-A(j\omega_0{}^\circ)F(j\omega_0{}^\circ)] = \operatorname{Arg}[L(j\omega_0{}^\circ)] = 0^\circ$$

Another convenient way to express this requirement is

$$Arg[-A(j\omega_{0dB})F(j\omega_{0dB})] = Arg[L(j\omega_{0dB})] > 0^{\circ}$$

where  $\omega_{0dB}$  is defined as

$$|A(j\omega_{0dB})F(j\omega_{0dB})| = |L(j\omega_{0dB})| = 1$$

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002

Lecture 120 - Compensation of Op Amps-I (1/26/04)

Page 120-4

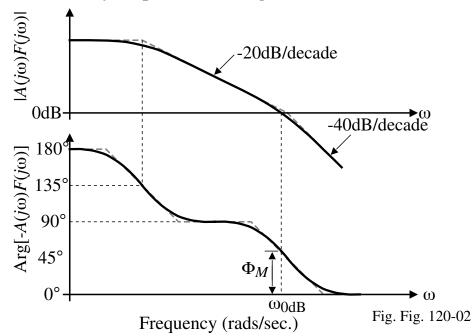

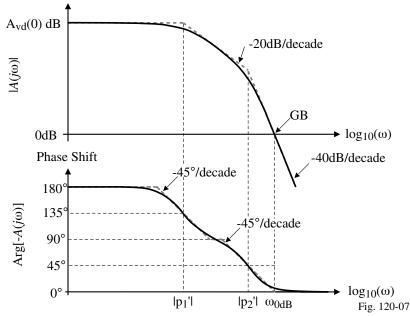

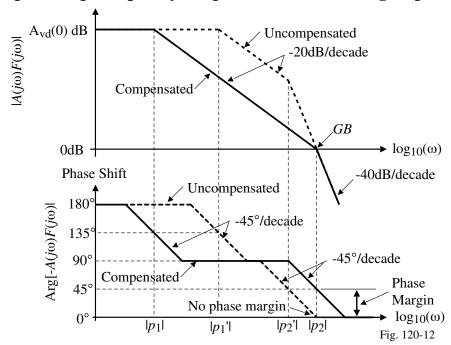

## **Illustration of the Stability Requirement using Bode Plots**

A measure of stability is given by the phase when  $|A(j\omega)F(j\omega)| = 1$ . This phase is called *phase margin*.

Phase margin =  $\Phi_M$  = Arg[- $A(j\omega_{0dB})F(j\omega_{0dB})$ ] = Arg[ $L(j\omega_{0dB})$ ]

## Why Do We Want Good Stability?

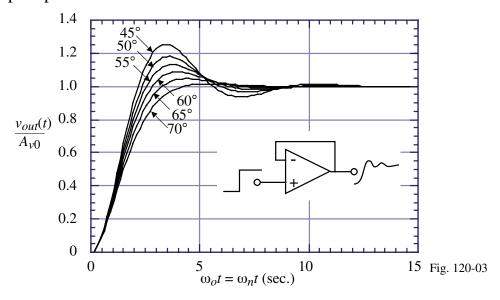

Consider the step response of second-order system which closely models the closed-loop gain of the op amp.

A "good" step response is one that quickly reaches its final value.

Therefore, we see that phase margin should be at least 45° and preferably 60° or larger. (A rule of thumb for satisfactory stability is that there should be less than three rings.)

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002

Lecture 120 - Compensation of Op Amps-I (1/26/04)

Page 120-6

## **Uncompensated Frequency Response of Two-Stage Op Amps**

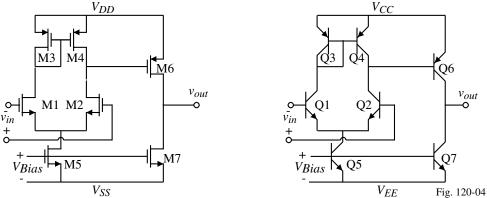

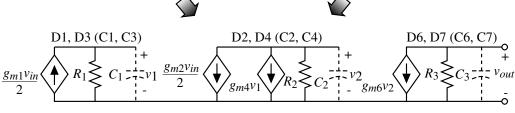

Two-Stage Op Amps:

Small-Signal Model:

Fig. 120-05

Note that this model neglects the base-collector and gate-drain capacitances for purposes of simplification.

ECE 6412 - Analog Integrated Circuit Design - II

## <u>Uncompensated Frequency Response of Two-Stage Op Amps - Continued</u>

For the MOS two-stage op amp:

$$R_1 \approx \frac{1}{g_{m3}} ||r_{ds3}||r_{ds1} \approx \frac{1}{g_{m3}}$$

$R_2 = r_{ds2} ||r_{ds4}||$

$$R_2 = r_{ds2} || r_{ds4}$$

and

$$R_3 = r_{ds6} || r_{ds7}$$

$$C_1 = C_{gs3} + C_{gs4} + C_{bd1} + C_{bd3}$$

$C_2 = C_{gs6} + C_{bd2} + C_{bd4}$  and  $C_3 = C_L + C_{bd6} + C_{bd7}$

$$C_2 = C_{gs6} + C_{bd2} + C_{bd4}$$

and

$$C_3 = C_L + C_{bd6} + C_{bd7}$$

For the BJT two-stage op amp:

$$\begin{split} R_1 &= \frac{1}{g_{m3}} \| r_{\pi 3} \| r_{\pi 4} \| r_{o1} \| r_{o3} \approx \frac{1}{g_{m3}} \ R_2 = r_{\pi 6} \| r_{o2} \| r_{o4} \approx r_{\pi 6} \quad \text{and} \quad R_3 = r_{o6} \| r_{o7} \\ C_1 &= C_{\pi 3} + C_{\pi 4} + C_{cs1} + C_{cs3} \qquad C_2 = C_{\pi 6} + C_{cs2} + C_{cs4} \quad \text{and} \quad C_3 = C_L + C_{cs6} + C_{cs7} \end{split}$$

$$R_2 = r_{\pi 6} || r_{o2} || r_{o4} \approx r_{\pi}$$

and

$$R_3 = r_{o6} || r_{o7}$$

$$C_1 = C_{\pi 3} + C_{\pi 4} + C_{cs1} + C_{cs3}$$

$$C_2 = C_{\pi 6} + C_{cs2} + C_{cs4}$$

and

$$C_3 = C_L + C_{cs6} + C_{cs7}$$

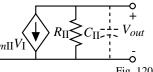

Assuming the pole due to  $C_1$  is much greater than the poles due to  $C_2$  and  $C_3$  gives,

The locations for the two poles are given by the following equations

$$p'_1 = \frac{-1}{R_{\rm I}C_{\rm I}}$$

and  $p'_2 = \frac{-1}{R_{\rm II}C_{\rm II}}$

where  $R_I(R_{II})$  is the resistance to ground seen from the output of the first (second) stage and  $C_I(C_{II})$  is the capacitance to ground seen from the output of the first (second) stage.

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002

Lecture 120 – Compensation of Op Amps-I (1/26/04)

Page 120-8

## **Uncompensated Frequency Response of an Op Amp**

If we assume that F(s) = 1 (this is the worst case for stability considerations), then the above plot is the same as the loop gain.

Note that the phase margin is much less than 45°.

Therefore, the op amp must be compensated before using it in a closed-loop configuration.

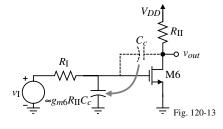

### **MILLER COMPENSATION**

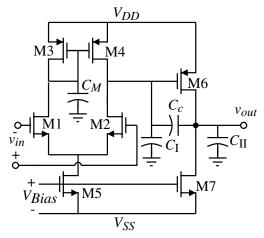

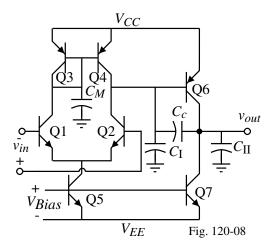

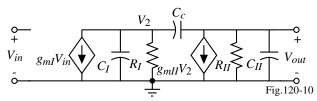

## **Two-Stage Op Amp**

The various capacitors are:

$C_c$  = accomplishes the Miller compensation

$C_M$  = capacitance associated with the first-stage mirror (mirror pole)

$C_I$  = output capacitance to ground of the first-stage

$C_{II}$  = output capacitance to ground of the second-stage

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002

Lecture 120 - Compensation of Op Amps-I (1/26/04)

Page 120-10

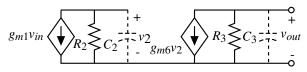

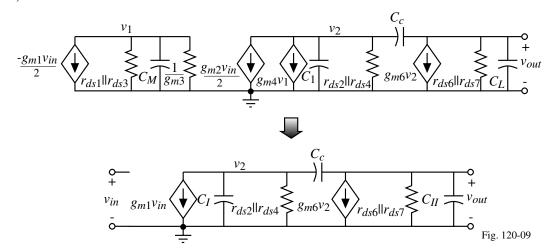

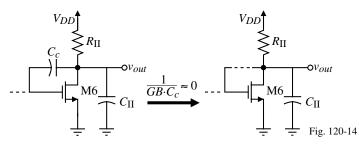

## Compensated Two-Stage, Small-Signal Frequency Response Model Simplified

Use the CMOS op amp to illustrate the above concept:

Assume:

$$g_{m3} >> g_{ds1} + g_{ds3}$$

and  $\frac{g_{m3}}{C_M} >> GB$

Therefore,

Same circuit holds for the BJT op amp with different component relationships.

## **Generalized Two-Stage Frequency Response Analysis**

where

$$g_{mI} = g_{m1} = g_{m2}, R_I = r_{ds2} || r_{ds4}, C_I = C_1$$

$$g_{mII} = g_{m6}, R_{II} = r_{ds6} || r_{ds7}, C_{II} = C_2 = C_L$$

**Nodal Equations:**

$$-g_{mI}V_{in} = [G_I + s(C_I + C_c)]V_2 - [sC_c]V_{out} \quad \text{and} \quad 0 = [g_{mII} - sC_c]V_2 + [G_{II} + sC_{II} + sC_c]V_{out}$$

Solving using Cramer's rule gives,

$$\frac{V_{out}(s)}{V_{in}(s)} = \frac{g_{ml}(g_{mll} - sC_c)}{G_lG_{ll} + s \left[G_{ll}(C_l + C_{ll}) + G_l(C_{ll} + C_c) + g_{mll}C_c\right] + s^2 \left[C_lC_{ll} + C_cC_l + C_cC_{ll}\right]}$$

$$= \frac{A_o \left[1 - s \left(C_c/g_{mll}\right)\right]}{1 + s \left[R_l(C_l + C_{ll}) + R_{ll}(C_2 + C_c) + g_{mll}R_lR_{ll}C_c\right] + s^2 \left[R_lR_{ll}(C_lC_{ll} + C_cC_l + C_cC_{ll})\right]}$$

where,  $A_o = g_{mI}g_{mII}R_IR_{II}$

In general,

$$D(s) = \left(1 - \frac{s}{p_1}\right) \left(1 - \frac{s}{p_2}\right) = 1 - s \left(\frac{1}{p_1} + \frac{1}{p_2}\right) + \frac{s^2}{p_1 p_2} \rightarrow D(s) \approx 1 - \frac{s}{p_1} + \frac{s^2}{p_1 p_2}, \text{ if } |p_2| >> |p_1|$$

$$\therefore \qquad p_1 = \frac{-1}{R_I(C_I + C_{II}) + R_{II}(C_{II} + C_c) + g_{mII}R_IR_{II}C_c} \approx \frac{-1}{g_{mII}R_IR_{II}C_c}, \qquad z = \frac{g_{mII}}{C_c}$$

$$\therefore p_{1} = \frac{-1}{R_{I}(C_{I} + C_{II}) + R_{II}(C_{II} + C_{c}) + g_{mII}R_{I}R_{II}C_{c}} \approx \frac{-1}{g_{mII}R_{I}R_{II}C_{c}}, z = \frac{g_{mII}}{C_{c}}, z = \frac{g_{mII}}{C_{c}}$$

$$p_{2} = \frac{-[R_{I}(C_{I}+C_{II})+R_{II}(C_{II}+C_{c})+g_{mII}R_{I}R_{II}C_{c}]}{R_{I}R_{II}(C_{I}C_{II}+C_{c}C_{I}+C_{c}C_{II})} \approx \frac{-g_{mII}C_{c}}{C_{I}C_{II}+C_{c}C_{I}+C_{c}C_{II}} \approx \frac{-g_{mII}}{C_{II}}, C_{II} > C_{c} > C_{I}$$

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002

Lecture 120 – Compensation of Op Amps-I (1/26/04)

Page 120-12

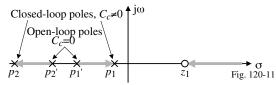

## Summary of Results for Miller Compensation of the Two-Stage Op Amp

There are three roots of importance:

1.) Right-half plane zero:

$$z_1 = \frac{gmII}{C_C} = \frac{gm6}{C_C}$$

This root is very undesirable- it boosts the magnitude while decreasing the phase.

2.) Dominant left-half plane pole (the Miller pole):

$$p_1 \approx \frac{-1}{g_{mII}R_IR_{II}C_c} = \frac{-(g_{ds2} + g_{ds4})(g_{ds6} + g_{ds7})}{g_{m6}C_c}$$

This root accomplishes the desired compensation.

3.) Left-half plane output pole:

$$p_2 \approx \frac{-8mII}{C_{II}} \approx \frac{-8m6}{C_{I}}$$

This pole must be  $\geq$  unity-gainbandwidth or the phase margin will not be satisfied. Root locus plot of the Miller compensation:

## Compensated Open-Loop Frequency Response of the Two-Stage Op Amp

Note that the unity-gainbandwidth, GB, is

$$GB = A_{vd}(0) \cdot |p_I| = (g_{mI}g_{mII}R_IR_{II}) \frac{1}{g_{mII}R_IR_{II}C_c} = \frac{g_{mI}}{C_c} = \frac{g_{m1}}{C_c} = \frac{g_{m2}}{C_c}$$

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002

Lecture 120 - Compensation of Op Amps-I (1/26/04)

Page 120-14

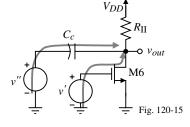

## **Conceptual Perspective of These Roots**

1.) The Miller pole:

$$|p_1| \approx \frac{1}{R_{\rm I}(g_{m6}R_{\rm II}C_c)}$$

2.) The left-half plane output pole:

$$|p_2| \approx \frac{g_{m6}}{C_{\text{II}}}$$

3.) Right-half plane zero (*Zeros always arise from multiple paths from the input to output*):

$$v_{out} = \left(\frac{-g_{m6}R_{II}(1/sC_c)}{R_{II} + 1/sC_c}\right)v' + \left(\frac{R_{II}}{R_{II} + 1/sC_c}\right)v'' = \frac{-R_{II}\left(\frac{g_{m6}}{sC_c} - 1\right)}{R_{II} + 1/sC_c}v$$

where  $v = v' = v''$ .

ECE 6412 - Analog Integrated Circuit Design - II

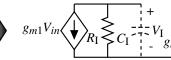

#### **Influence of the Mirror Pole**

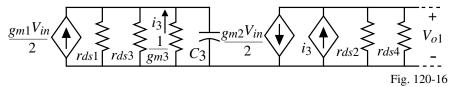

Up to this point, we have neglected the influence of the pole,  $p_3$ , associated with the current mirror of the input stage. A small-signal model for the input stage that includes  $C_3$  is shown below:

The transfer function from the input to the output voltage of the first stage,  $V_{o1}(s)$ , can be written as

$$\frac{V_{o1}(s)}{V_{in}(s)} = \frac{-g_{m1}}{2(g_{ds2} + g_{ds4})} \left[ \frac{g_{m3} + g_{ds1} + g_{ds3}}{g_{m3} + g_{ds1} + g_{ds3} + sC_3} + 1 \right] \approx \frac{-g_{m1}}{2(g_{ds2} + g_{ds4})} \left[ \frac{sC_3 + 2g_{m3}}{sC_3 + g_{m3}} \right]$$

We see that there is a pole and a zero given as

$$p_3 = -\frac{g_{m3}}{C_3}$$

and  $z_3 = -\frac{2g_{m3}}{C_3}$

Because the pole and zero are an octave away from each other and because these roots are much larger, the influence of the mirror pole (zero) can be neglected.

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002

Lecture 120 – Compensation of Op Amps-I (1/26/04)

Page 120-16

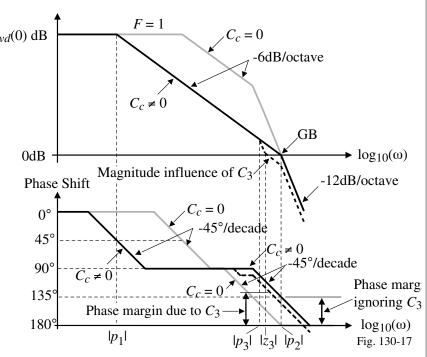

#### <u>Influence of the Mirror Pole – Continued</u>

Fortunately, the presence of the zero tends to negate the effect of the pole. Generally, the pole and zero due to  $C_3$  is greater than GB and will have very little influence on the stability of the two-stage op amp.

The plot shown illustrates  $A_{vd}(0) dB$  the case where these roots are less than GB and even then they have little effect on stability.

In fact, they actually increase the phase margin slightly because *GB* is decreased.

## **SUMMARY**

## Compensation

- Designed so that the op amp with unity gain feedback (buffer) is stable

- Types

- Miller

- Miller with nulling resistors

- Self Compensating

- Feedforward

ECE 6412 - Analog Integrated Circuit Design - II

© P.E. Allen - 2002